NOT RECOMMENDED FOR NEW DESIGNS **Contact our Technical Support Center at** 1-888-INTERSIL or www.intersil.com/tsc

ww.intersil.com/products/TW2871

FN7989 Rev. 1.00 December 20, 2012

Fisheye Distortion Correction LSI with Built-in Image Signal Processor, Motion Detector and DDR2 Controller

The TW2871 is a highly integrated fisheye distortion correction LSI with built-in Image Signal Processor, Motion detector and DDR2 Controller for both network and analog cameras. The TW2871 can pan, tilt and zoom without mechanical moving parts. The TW2871 supports one HD(1080i) digital output and four SD analog outputs.

### **Features**

#### **Host Interface**

- 4-bit address and 8-bit parallel data interface

- 16 byte slave registers

- Supports two kinds of extended cycle access (external wait pin and register handshake mode)

- Auto address increment mode

#### **Image Signal Processor**

- Supports Bayer format and external ISP input

- Black level correction

- Gamma correction

- Lens shading correction

- Noise reduction

- Edge enhancement

- Wide dynamic range

### **Geometric Engine**

- . Digital Pan, Tilt and Zoom

- Up to 4 distortion corrected windows and one fisheye window

- Supports one HD digital output or 2 SD digital

- Supports 4 SD analog outputs

#### **DSP**

- Harvard architecture (Instruction: 24-bit, Data: 24-bit)

- 24-bit multiplier, 56-bit ALU

- 144 instructions including SIMD and special purpose functions

- Branch predictor for high hit rate

- 56-bit accumulator file

- Power saving mode achieved by sleep instruction

#### **Motion Detector**

- Detection for Motion (MD), Blind (BD, such as covered by something on purpose)

- Large input size: 5M (2592x1944) or 8M (3264x2448) CIS

- Detection element 32x24, each mesh can be maskable

- Supports Motion detection speed control and manual strobe

- Fine adjustments by several thresholds programmed by internal registers

#### **DDR2 Interface**

- Compatible with JEDEC DDR2 specification (JESD79-2C)

- Speed bin from 250 to 667MHz at DDR

- Supports OCD calibration

- 64 Byte internal buffers, which follow MESI algorithm to utilize high data locality

- Supports data pre-fetch mechanism to maximize data throughput

#### OSD

- Embedded RAM based OSD

- Up to 8 OSD windows

- Up to 256 fonts

#### OSG

- External memory (DDR2) based OSG

- Up to 8 OSG windows

- Supports transparent color

## **Applications**

- Security surveillance camera

- Drive monitor

- Drive recorder

## Related Literature

- TW2871 Hardware Application Note

- TW2871 Software Application Note

- TW2871 Programmer Note

- TW2871 Command Manual

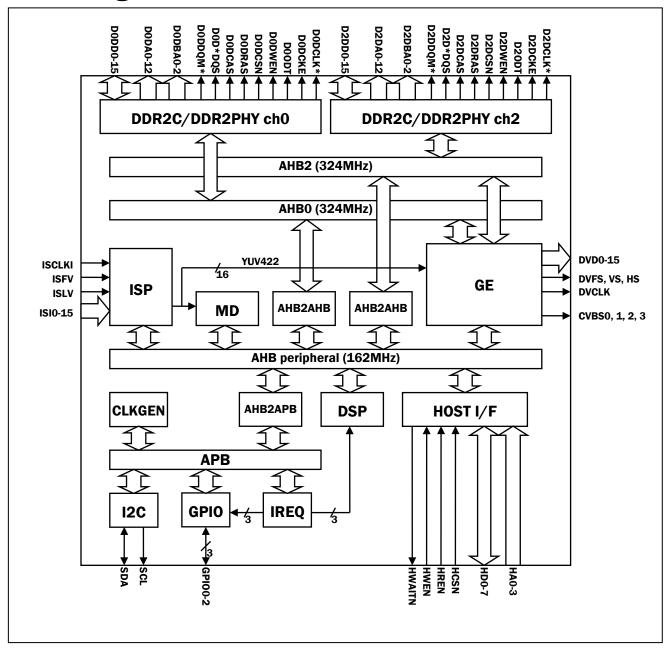

# **Block Diagram**

© Copyright Intersil Americas LLC 2012. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

in the quality certifications found at http://www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="http://www.intersil.com">http://www.intersil.com</a>