- **EIA-170 Timing Operation**

- Solid-State Reliability

- **Fixed Electronic-Shutter Options**

- **Random Shutter-Mode**

- Flicker-Compensation Mode

- **Auto-Iris Capability**

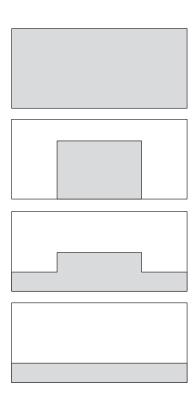

- **Electronic-Windowing Options**

- **Horizontal and Vertical Resets for External** Synchronization 5 4 1

- **Double-Speed Readout Option**

### description

The TMC57750 is a monolithic integrated circuit designed to supply timing signals for the Texas Instruments (TI™) 4-mm TC255 monochrome CCD image sensor. The TMC57750 supplies both CCD drive signals and EIA-170 television-synchronization signals at standard video rates. It requires a single 5-V supply voltage and a 25-MHz timing crystal or crystal oscillator. The TMC57750 provides the user with several options including antiblooming-frequency selection, external synchronization, fixed electronic-shutter selection, electronic auto-iris, and window selection.

The TMC57750 is designed to drive the TC255 CCD image sensor through an intermediary level-shifting device such as the TI TMC57253 serial and parallel driver. It supplies sampling, clamping, and synchronizing signals for the TI SN76121OFR video processor. The TMC57750 EIA-170 synchronization signals include composite sync, composite blank, and field indicator.

The TMC57750 is supplied in a 64-pin plastic flat package and is characterized for operation from -20°C to 45°C.

TI is a trademark of Texas Instruments Incorporated.

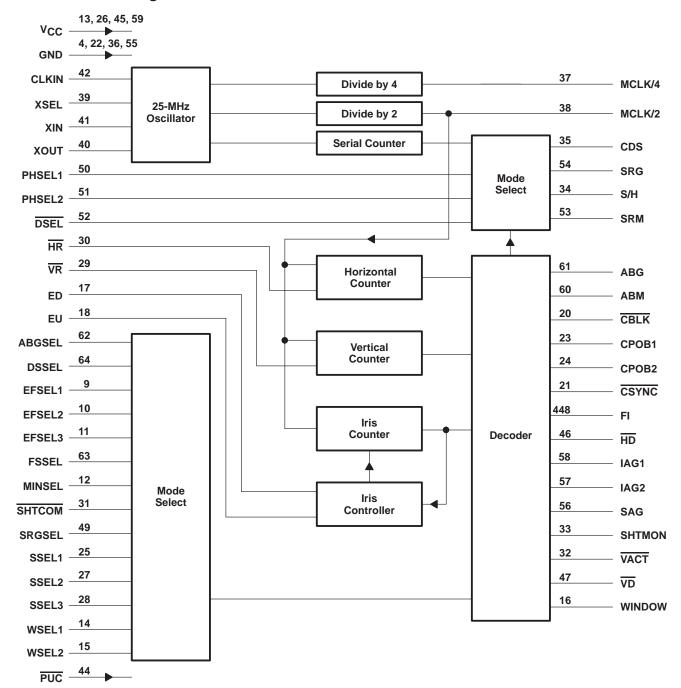

## functional block diagram

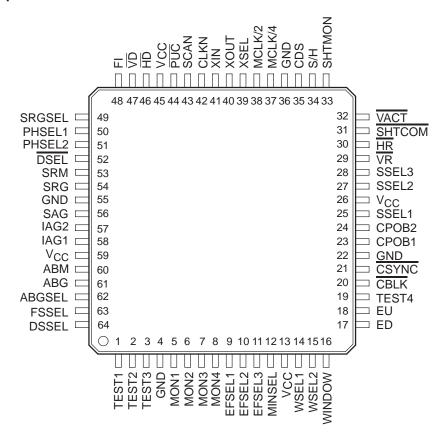

## **Terminal Functions**

| TERMINAL                     |                  |     |                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                         | NO.              | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ABG                          | 61               | 0   | Antiblooming gate                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ABM                          | 60               | 0   | Antiblooming gate mid-level                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ABGSEL                       | 62               | I   | Antiblooming-gate select. ABGSEL selects the frequency of the antiblooming gate. When ABGSE is high, the standard frequency of 6.25 MHz is selected. When low, the double frequency of 12. MHz is selected.                                                                                                                                                         |  |  |  |

| CLKIN                        | 42               | ı   | Clock in                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| CBLK                         | 20               | 0   | Composite blank                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| CPOB1                        | 23               | 0   | Optical black clamp one                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CPOB2                        | 24               | 0   | Optical black clamp two                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CSYNC                        | 21               | 0   | Composite sync                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| CDS                          | 35               | 0   | Co9rrelated double sampling                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| DSEL                         | 52               | ı   | Delay select. DSEL selects the delay of CDS and S/H with respect to SRG. When DSEL is high, a standard delay is selected. When low, an additional delay of 5 ns is selected.                                                                                                                                                                                        |  |  |  |

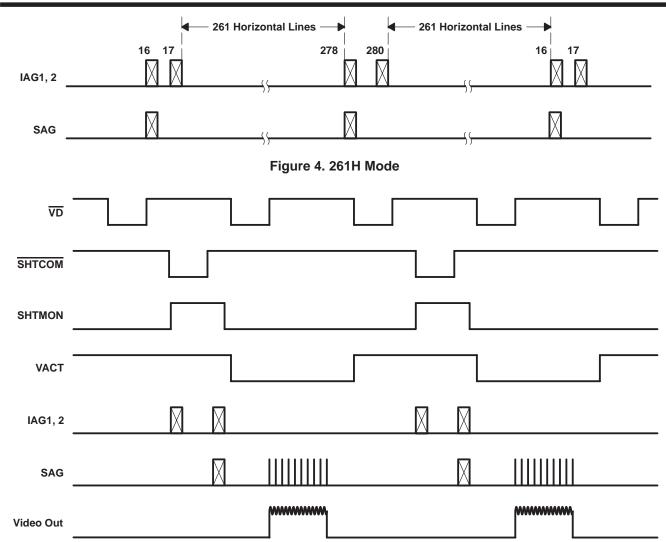

| DSSEL                        | 64               | I   | Display-scan select. DSSEL selects the display-scanning mode. When DSSEL is high, the interlace mode is selected. When low, the noninterlace mode is selected. In the interlace mode, one field is 262.5 horizontal lines and one frame is 525 horizontal lines. In the noninterlace mode, one field is 262 horizontal lines and one frame is 524 horizontal lines. |  |  |  |

| ED                           | 17               | ı   | Exposure down. ED decreases the integration of the CCD sensor.                                                                                                                                                                                                                                                                                                      |  |  |  |

| EU                           | 18               | ı   | Exposure up. EU increases the integration of the CCD sensor.                                                                                                                                                                                                                                                                                                        |  |  |  |

| EFSEL1,<br>EFSEL2,<br>EFSEL3 | 9, 10, 11        | I   | Electronic-function select. EFSEL1, EFSEL2, and EFSEL3 selects the operational modes (see Table 1 and Figure 4).                                                                                                                                                                                                                                                    |  |  |  |

| FI                           | 49               | 0   | Field index                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| FSSEL                        | 63               | ı   | Frame-shift select. FSSEL selects the parallel-transfer frequency. When FSSEL is high, the standard frequency of 12.5 MHz is selected. When low, the double frequency of 25 MHz is selected.                                                                                                                                                                        |  |  |  |

| GND                          | 4, 22, 36,<br>55 |     | Ground                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| HD                           | 46               | 0   | Horizontal drive                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| HR                           | 30               | I   | Horizontal reset                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| IAG1                         | 58               | 0   | Image-area gate 1                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IAG2                         | 57               | 0   | Image-area gate 2                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| MCLK/4                       | 37               | 0   | Master clock divided by 4                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| MCLK/2                       | 38               | 0   | Master clock divided by 2                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| MINSEL                       | 12               | I   | Minimum exposure-time select. MINSEL selects the minimum exposure time for the auto-iris mode. When high, the exposure time of 1/50000 second is selected. When low, the exposure time of 1/8000 second is selected.                                                                                                                                                |  |  |  |

| MON1, MON2,<br>MON3, MON4    | 5, 6,<br>7, 8    | 0   | MON1, MON2, MON3, and MON4 are test-monitoring terminals and are not used in normal operation.                                                                                                                                                                                                                                                                      |  |  |  |

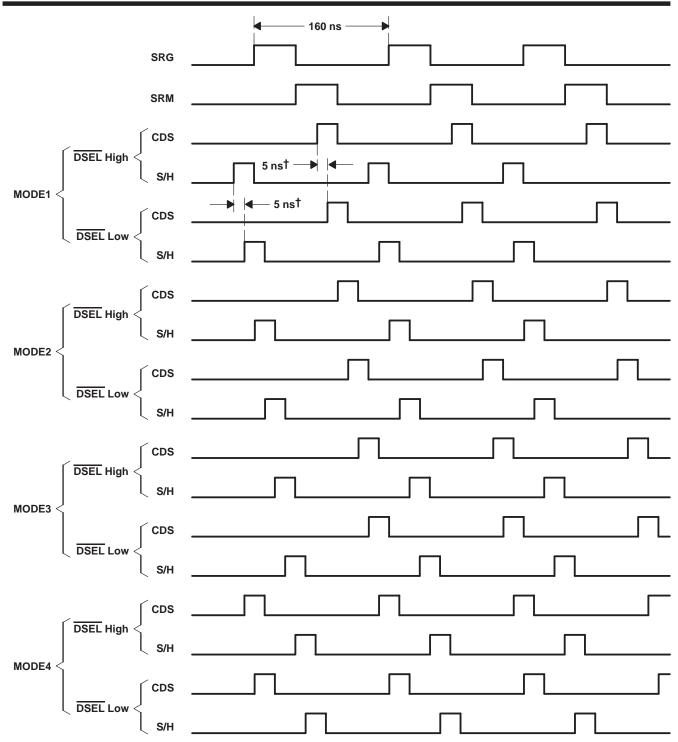

| PHSEL1,<br>PHSEL2            | 50, 51           | I   | Phase select. PHSEL1 and PHSEL2 determine the timing relation of S/H and CDS with respect to SRG.  PHSEL1 PHSEL2 OPERATION  H H MODE1  L H MODE2  H L MODE3  L L MODE4  MODES1, 2, 3, and 4 are shown in Figure 3.                                                                                                                                                  |  |  |  |

## **Terminal Functions (Continued)**

| TERMINAL                      |                   | 1/0 | DECORPORTION                                                                                                                                                                                                                                                  |  |  |

|-------------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                          | NO.               | I/O | DESCRIPTION                                                                                                                                                                                                                                                   |  |  |

| PUC                           | 44                | I   | Power-up clear                                                                                                                                                                                                                                                |  |  |

| SAG                           | 56                | 0   | torage-area gate                                                                                                                                                                                                                                              |  |  |

| SCAN                          | 43                |     | SCAN is a test point and is not used in normal operation.                                                                                                                                                                                                     |  |  |

| SHTCOM                        | 31                | I   | Shutter command                                                                                                                                                                                                                                               |  |  |

| SRG                           | 54                | 0   | Serial-register gate                                                                                                                                                                                                                                          |  |  |

| SRM                           | 53                | 0   | Serial-register gate mid-level                                                                                                                                                                                                                                |  |  |

| SRGSEL                        | 49                | I   | Serial-register gate select. SRGSEL selects the readout frequency. When SRGSEL is high, the standard frequency of 6.25 MHz is selected. When low, the double frequency of 12.5 MHz is selected.                                                               |  |  |

| SHTMON                        | 33                | 0   | Shutter monitor                                                                                                                                                                                                                                               |  |  |

| S/H                           | 34                | 0   | Sample and hold                                                                                                                                                                                                                                               |  |  |

| SEL1,<br>SEL2,<br>SEL3        | 25, 27, 28        | I   | Shutter-speed select. SEL1, SEL2, and SEL3 selects the fixed shutter times in horizontal TV lines. This selection sets the exposure times if either the manual-shutter or random-shutter modes are selected (see Table 2).                                    |  |  |

| TEST1, TEST2,<br>TEST3, TEST4 | 1, 2,<br>3, 19    |     | TEST1, TEST2, TEST3, and TEST4 are test points and are not used in normal operation.                                                                                                                                                                          |  |  |

| VACT                          | 32                | 0   | Video active                                                                                                                                                                                                                                                  |  |  |

| VCC                           | 13, 26,<br>45, 59 |     | Supply voltage                                                                                                                                                                                                                                                |  |  |

| VD                            | 47                | 0   | Vertical drive                                                                                                                                                                                                                                                |  |  |

| VR                            | 29                | I   | Vertical reset                                                                                                                                                                                                                                                |  |  |

| WINDOW                        | 16                | 0   | Window. WINDOW is high as defined by WSEL1 and WSEL2 at the times in TV lines and horizontal pixels (see Table 3).                                                                                                                                            |  |  |

| WSEL1,<br>WSEL2               | 14, 15            | I   | Window select. WSEL1 and WSEL2 selects the output mode of WINDOW. These inputs are normally used with the auto-iris mode in selecting the desired region to optimize the exposure of the best image (see Table 3).  WSEL1 WSEL2 OPERATION H H MODE1 L H MODE2 |  |  |

|                               |                   |     | H L MODE3 L L MODE4                                                                                                                                                                                                                                           |  |  |

| XSEL                          | 39                | I   | Crystal-oscillator select. XSEL selects the inputs used as the master clock. When XSEL is high, a 25-MHz crystal is connected between XIN and XOUT. When XSEL is low, a 25-MHz crystal oscillator is required and its output connected to CLKIN.              |  |  |

| XIN                           | 41                |     | Crystal in                                                                                                                                                                                                                                                    |  |  |

| XOUT                          | 40                |     | Crystal out                                                                                                                                                                                                                                                   |  |  |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub>                        | 0.5 V to 6 V                                      |

|--------------------------------------------------------------|---------------------------------------------------|

| Input voltage range, V <sub>I</sub>                          | $\cdots -0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$ |

| Output voltage range, VO                                     | $-0.5 \text{ V to V}_{CC} + 0.5 \text{ V}$        |

| Operating free-air temperature range, T <sub>A</sub>         | –20°C to 45°C                                     |

| Storage temperature range, T <sub>STG</sub>                  | 65°C to 150°C                                     |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |                                                   |

## recommended operating conditions

|                                 |                                |      | MIN                | NOM | MAX                | UNIT |

|---------------------------------|--------------------------------|------|--------------------|-----|--------------------|------|

| Vcc                             | CC Supply voltage              |      |                    | 5   | 5.5                | V    |

| V                               | High level input voltage       | TTL  | 2                  |     | VCC                | · v  |

| VIH                             | High-level input voltage       | CMOS | 0.7V <sub>CC</sub> |     | VCC                |      |

| VIL                             | Low-level input voltage        | TTL  | GND                |     | 0.8                | V    |

|                                 |                                | CMOS | GND                |     | 0.2V <sub>CC</sub> |      |

| 4.4.                            | lanut sign and fall times      | TTL  | 0                  |     | 25                 |      |

| t <sub>r</sub> , t <sub>f</sub> | Input rise and fall times      | CMOS | 0                  |     | 25                 | ns   |

| T <sub>A</sub>                  | Operating free-air temperature | -    | -20                |     | 45                 | °C   |

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER        |                                        | TEST CONDITIONS                         | MIN                  | MAX | UNIT |

|------------------|----------------------------------------|-----------------------------------------|----------------------|-----|------|

| Vон              | High-level output voltage              | IOH = Rated current                     | V <sub>CC</sub> -0.8 |     | V    |

| VOL              | Low-level output voltage               | I <sub>OL</sub> = Rated current         |                      | 0.5 | V    |

| V <sub>T+</sub>  | Schmitt-trigger input hysteresis, TTL  | V                                       | 0.3                  |     | V    |

| V <sub>T</sub> – | Schmitt-trigger input hysteresis, CMOS | V <sub>CC</sub> = 5 V                   | 0.2V <sub>CC</sub>   |     | V    |

| lн               | High-level input current               | $V_I = V_{CC}$                          |                      | 1   | μΑ   |

| I <sub>I</sub> L | Low-level input current                | V <sub>I</sub> = GND                    |                      | -1  | μΑ   |

| IO               | Output current                         | V <sub>O</sub> = V <sub>CC</sub> or GND |                      | ±10 | μΑ   |

| Iccq             | Quiescent current                      | $V_I = V_{CC}$                          |                      | 60  | μΑ   |

**Table 1. Electronic-Function Select**

| EFSEL1 | EFSEL2 | EFSEL3 | MODE              |  |  |

|--------|--------|--------|-------------------|--|--|

| L      | L      | L      | 261H <sup>†</sup> |  |  |

| Н      | L      | L      | Auto-iris‡        |  |  |

| L      | Н      | L      | Random shutter    |  |  |

| Н      | Н      | L      | Flickerless§      |  |  |

| L      | L      | Н      | Manual shutter    |  |  |

| Н      | L      | Н      | STD               |  |  |

| L      | Н      | Н      | STD               |  |  |

| Н      | Н      | Н      | STD               |  |  |

<sup>†</sup> For the 261H mode, see Figure 4.

Table 2. Shutter-Speed Select

| SEL1 | SEL2 SEL3 |   | FIXED<br>SHUTTER TIMES |

|------|-----------|---|------------------------|

| L    | L         | L | 1H                     |

| Н    | L         | L | 2H                     |

| L    | Н         | L | 4H                     |

| Н    | Н         | L | 8H                     |

| L    | L         | Н | 16H                    |

| Н    | L         | Н | 32H                    |

| L    | Н         | Н | 64H                    |

| Н    | Н         | Н | 128H                   |

<sup>&</sup>lt;sup>‡</sup> The maximum range of the auto-iris integration times is 1/50000 second to 1/60 second

<sup>§</sup> The flickerless mode has a fixed shutter of 1/100 second. It has an effect only when 50-Hz pwer systems are in use.

### **Table 3. WINDOW Modes**

| MODE                   | PIXEL   |         |         |  |

|------------------------|---------|---------|---------|--|

| MODE                   | 130-294 | 295-624 | 625–789 |  |

| MODE1                  |         |         |         |  |

| Lines 22-81, 285-344   | Н       | Н       | Н       |  |

| Lines 82-141, 345-404  | Н       | Н       | Н       |  |

| Lines 142-201, 405-464 | Н       | Н       | Н       |  |

| Lines 202-261, 465-525 | Н       | Н       | Н       |  |

| MODE2                  |         |         |         |  |

| Lines 22-81, 285-344   | L       | L       | L       |  |

| Lines 82–141, 345–404  | L       | Н       | L       |  |

| Lines 142-201, 405-464 | L       | Н       | L       |  |

| Lines 202-261 465-525  | L       | Н       | L       |  |

| MODE3                  |         |         |         |  |

| Lines 22-81, 285-344   | L       | L       | L       |  |

| Lines 82-141, 345-404  | L       | L       | L       |  |

| Lines 142-201, 405-464 | L       | Н       | L       |  |

| Lines 202-261 465-525  | Н       | Н       | Н       |  |

| MODE4                  |         |         |         |  |

| Lines 22-81, 285-344   | L       | L       | L       |  |

| Lines 82-141, 345-404  | L       | L       | L       |  |

| Lines 142-201, 405-464 | L       | L       | L       |  |

| Lines 202–261, 465–525 | Н       | Н       | Н       |  |

†One TV frame = 33.3 ms = 525 intervals

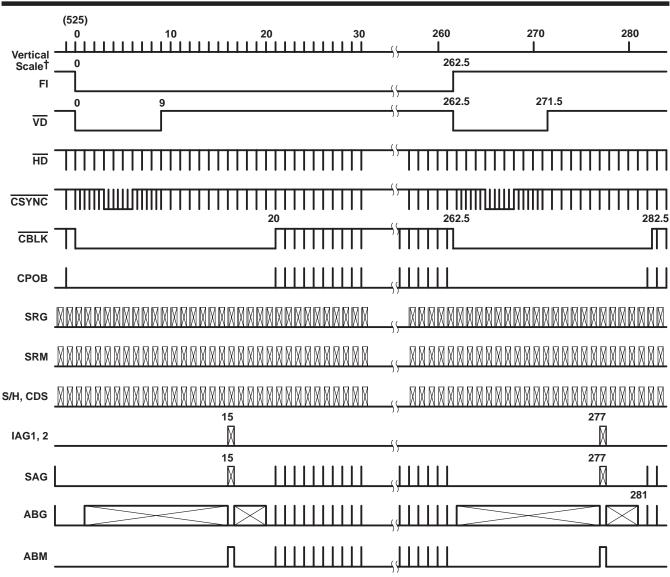

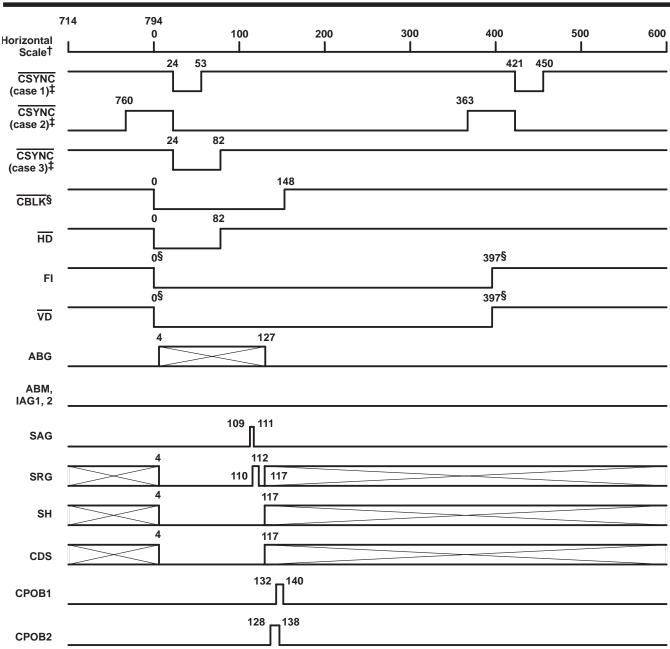

Figure 1. Vertical Timing

<sup>†</sup>One horizontal-scan line = 63.52 µs = 794 intervals

**Figure 2. Horizontal Timing**

<sup>‡</sup> CSYNC varies depending on which horizontal-scan line of a 262.5-line TV field is being examined.

<sup>•</sup> Case 1 depicts the equalization pulses that occur during horizontal-scan lines 1, 2, 3, 7, 8, and 9.

<sup>•</sup> Case 2 depicts the vertical serration pulses that occur during horizontal-scan lines 4, 5, and 6.

<sup>•</sup> Case 3 applies to all remaining horizontal-scan lines.

<sup>§</sup> CBLK makes 1/2 line transitions only on lines 262.5 and 268.5. FI makes a high-to-low transition only on line 525 and a low-to-high transition only on line 262.5. VD makes high to low transitions only on lines 525 and 262.5. It makes low-to-high transitions only on lines 9 and 271.5.

<sup>†</sup> In all four modes, the selection of DSEL low results in an additional 5-ns delay of CDS and S/H with respect to SRG.

Figure 3. Phase-Select-Mode Timing

Figure 5. Random-Shutter-Mode Timing

<sup>†</sup> One horizontal-scan line = 63.52 μs = 794 intervals

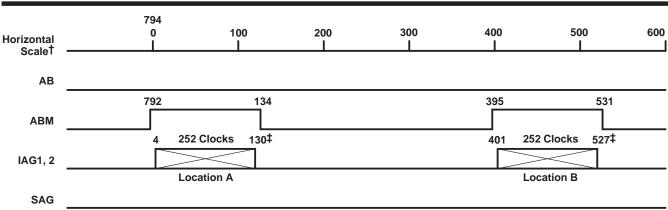

794 100 200 300 400 500 600 0 Horizontal Scale<sup>†</sup> AB 268 **ABM** 244 Clocks IAG1, 2‡ 244 Clocks SAG‡ 244 Clocks SRG‡ IAG1, 2

Figure 6. Clear Timing

<sup>‡</sup> The frequency of the parallel transfer is 12.5 MHz.

Figure 7. Parallel-Transfer Timing

<sup>‡</sup> The clear sequence must take place at Location A if the iris controller determines that it is to be executed on any of the lines 21–262 of TV field 1 or lines 284–525 of TV field 2. The clear sequence can take place at either Location A or Location B if the iris controller determines that it is to be executed on any of the lines 1-20 (excluding line 16) of TV field 1 or lines 263-283 (excluding line 278) of TV field 2. The frequency of the clear sequence is 25 MHz.

<sup>†</sup> One horizontal-scan line =  $63.52 \,\mu s$  =  $794 \,intervals$

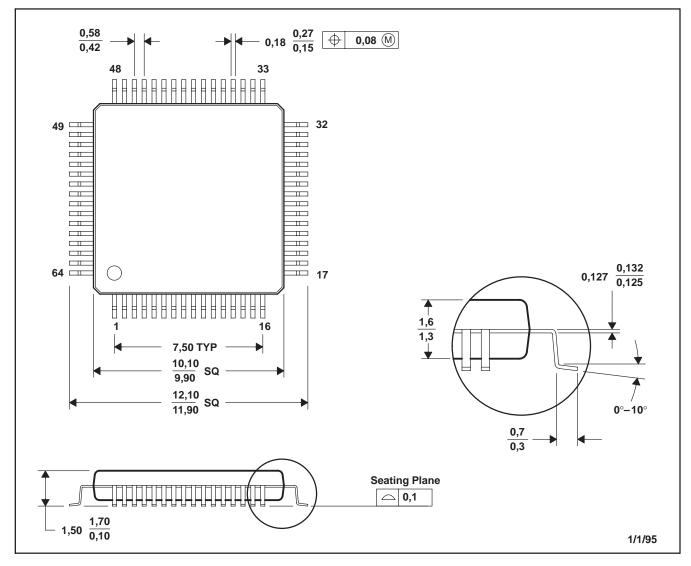

### **MECHANICAL DATA**

## LQFP

### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated