## S-8259A Series

www.ablicinc.com

## **BATTERY MONITORING IC FOR 1-CELL PACK**

© ABLIC Inc., 2015-2017 Rev.1.1\_01

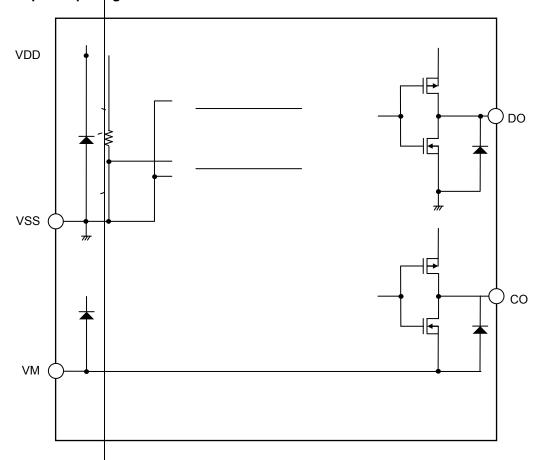

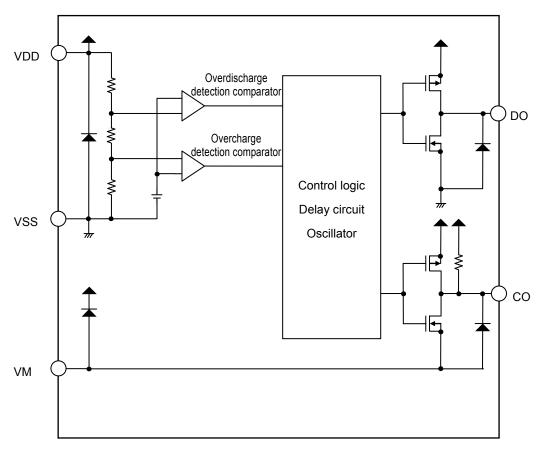

## **■** Block Diagram

1. CO pin output logic active "H"

## 2. CO pin output logic active "L"

Figure 2

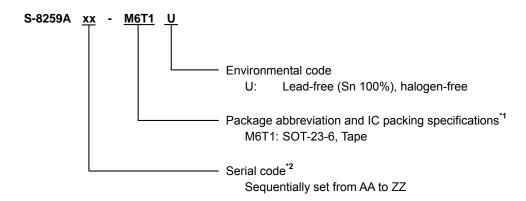

## **■ Product Name Structure**

## 1. Product name

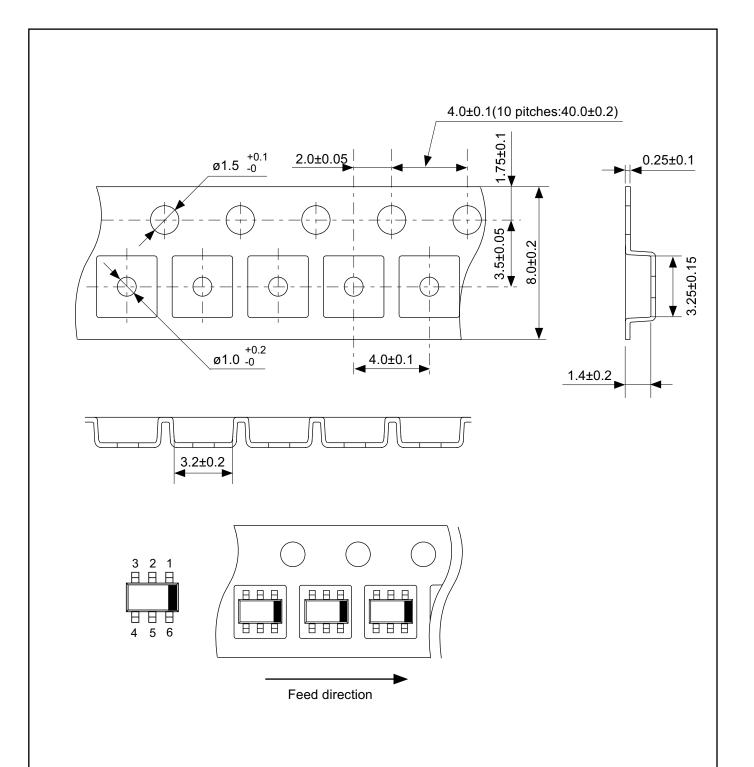

- \*1. Refer to the tape drawing.

- \*2. Refer to "3. Product name list".

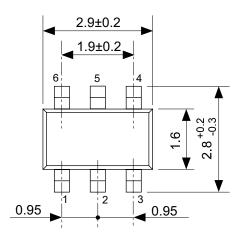

### 2. Package

**Table 1 Package Drawing Codes**

| Table 1 1 denage Plawing Codes |              |              |              |  |  |  |

|--------------------------------|--------------|--------------|--------------|--|--|--|

| Package Name                   | Dimension    | Tape         | Reel         |  |  |  |

| SOT-23-6                       | MP006-A-P-SD | MP006-A-C-SD | MP006-A-R-SD |  |  |  |

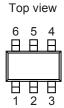

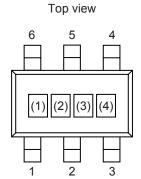

## **■** Pin Configuration

## 1. SOT-23-6

Figure 3

Table 4

| Pin No. | Symbol           | Description                                          |

|---------|------------------|------------------------------------------------------|

| 1       | DO               | Output pin for overdischarge detection (CMOS output) |

| 2       | VM               | Negative power supply input pin for CO pin           |

| 3       | СО               | Output pin for overcharge detection (CMOS output)    |

| 4       | NC <sup>*1</sup> | No connection                                        |

| 5       | VDD              | Input pin for positive power supply                  |

| 6       | VSS              | Input pin for negative power supply                  |

<sup>\*1.</sup> The NC pin is electrically open.

The NC pin can be connected to VDD pin or VSS pin.

## **■** Electrical Characteristics

1. Ta = +25°C

Table 6

(Ta = +25°C unless otherwise specified)

| Item                                          | Symbol            | Condition                                      | Min.                      | Тур.            | Max.                       | Unit | Test<br>Circuit |  |

|-----------------------------------------------|-------------------|------------------------------------------------|---------------------------|-----------------|----------------------------|------|-----------------|--|

| Detection Voltage                             |                   |                                                |                           |                 |                            |      |                 |  |

| Overall arms detection valters                |                   | _                                              | $V_{\text{CU}}-0.020$     | V <sub>CU</sub> | $V_{CU} + 0.020$           | V    | 1               |  |

| Overcharge detection voltage                  | V <sub>CU</sub>   | $Ta = -10^{\circ}C \sim +60^{\circ}C^{*1}$     | $V_{\text{CU}}-0.025$     | V <sub>CU</sub> | $V_{CU} + 0.025$           | V    | 1               |  |

| Overall area valle as                         | Va                | V <sub>CL</sub> ≠ V <sub>CU</sub>              | $V_{\text{CL}}-0.050$     | V <sub>CL</sub> | V <sub>CL</sub> + 0.050    | V    | 1               |  |

| Overcharge release voltage                    | $V_{CL}$          | V <sub>CL</sub> = V <sub>CU</sub>              | $V_{\text{CL}}-0.025$     | V <sub>CL</sub> | V <sub>CL</sub> + 0.020    | V    | 1               |  |

| Overdischarge detection voltage               | $V_{DL}$          | -                                              | $V_{DL}-0.050$            | $V_{DL}$        | $V_{DL} + 0.050$           | V    | 2               |  |

| Overdischarge release voltage                 | $V_{DU}$          | $V_{DL} \neq V_{DU}$                           | $V_{DU}-0.100$            | $V_{DU}$        | $V_{DU} + 0.100$           | V    | 2               |  |

| Input Voltage                                 |                   |                                                |                           |                 |                            |      |                 |  |

| Operation voltage between VDD pin and VSS pin | $V_{DSOP}$        | _                                              | 1.5                       | -               | 6.0                        | ٧    | _               |  |

| Input Current                                 | I                 |                                                |                           |                 |                            |      | 1               |  |

| Current consumption during operation          | I <sub>OPE</sub>  | $V_{DD} = 3.4 \text{ V}, V_{VM} = 0 \text{ V}$ | _                         | 1.5             | 3.0                        | μА   | 3               |  |

| Current consumption during overdischarge      | I <sub>OPED</sub> | $V_{DD} = 1.5 \text{ V}, V_{VM} = 0 \text{ V}$ | -                         | _               | 2.0                        | μΑ   | 3               |  |

| Output Resistance                             |                   |                                                |                           |                 |                            |      |                 |  |

| CO pin resistance "H" 1                       | R <sub>COH1</sub> | -                                              | 5                         | 10              | 20                         | kΩ   | 4               |  |

| CO pin resistance "L" 1                       | R <sub>COL1</sub> | -                                              | 5                         | 10              | 20                         | kΩ   | 4               |  |

| DO pin resistance "H"                         | R <sub>DOH</sub>  | -                                              | 5                         | 10              | 20                         | kΩ   | 4               |  |

| DO pin resistance "L"                         | R <sub>DOL</sub>  | -                                              | 5                         | 10              | 20                         | kΩ   | 4               |  |

| CO pin resistance "H" 2                       | R <sub>COH2</sub> | Active "L"                                     | 1                         | 4               | _                          | MΩ   | 4               |  |

| CO pin resistance "L" 2                       | R <sub>COL2</sub> | Active "H"                                     | 1                         | 4               | _                          | MΩ   | 4               |  |

| Delay Time                                    |                   |                                                |                           |                 |                            |      |                 |  |

| Overcharge detection delay time               | tcu               | -                                              | $t_{\text{CU}}\times 0.7$ | tcu             | $t_{\text{CU}} \times 1.3$ | -    | 5               |  |

| Overcharge release delay time                 | t <sub>CL</sub>   | -                                              | $t_{\text{CL}}\times 0.7$ | t <sub>CL</sub> | $t_{\text{CL}}\times 1.3$  | _    | 5               |  |

| Overdischarge detection delay time            | t <sub>DL</sub>   |                                                | $t_{\text{DL}}\times 0.7$ | $t_{DL}$        | $t_{\text{DL}}\times 1.3$  | _    | 5               |  |

<sup>\*1.</sup> Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

## 2. Ta = $-40^{\circ}$ C to $+85^{\circ}$ C<sup>\*1</sup>

Table 7

(Ta = -40°C to +85°C<sup>\*1</sup> unless otherwise specified)

| ltem                                                               | Symbol                                | Condition                                      | Min.                      | Тур.            | Max.                       | Unit      | Test<br>Circuit |  |

|--------------------------------------------------------------------|---------------------------------------|------------------------------------------------|---------------------------|-----------------|----------------------------|-----------|-----------------|--|

| Detection Voltage                                                  |                                       |                                                |                           |                 |                            |           |                 |  |

| Overcharge detection voltage                                       | Vcu                                   | -                                              | V <sub>CU</sub> - 0.045   | V <sub>CU</sub> | V <sub>CU</sub> +0.030     | V         | 1               |  |

| 0                                                                  | V                                     | $V_{CL} \neq V_{CU}$                           | $V_{CL}-0.080$            | $V_{CL}$        | V <sub>CL</sub> + 0.060    | V         | 1               |  |

| Overcharge release voltage                                         | $V_{CL}$                              | V <sub>CL</sub> = V <sub>CU</sub>              | $V_{CL} - 0.050$          | $V_{CL}$        | V <sub>CL</sub> + 0.030    | ٧         | 1               |  |

| Overdischarge detection voltage                                    | $V_{DL}$                              | _                                              | $V_{DL}-0.080$            | $V_{DL}$        | $V_{DL} + 0.060$           | ٧         | 2               |  |

| Overdischarge release voltage                                      | $V_{DU}$                              | $V_{DL} \neq V_{DU}$                           | $V_{DU} - 0.130$          | $V_{DU}$        | V <sub>DU</sub> + 0.110    | V         | 2               |  |

| Input Voltage                                                      |                                       |                                                |                           |                 |                            |           |                 |  |

| Operation voltage between VDD pin and VSS pin                      | Operation voltage between VDD pin and |                                                | 1.5                       | _               | 6.0                        | ٧         | -               |  |

| Input Current                                                      |                                       |                                                |                           |                 |                            |           |                 |  |

| Current consumption during operation                               | I <sub>OPE</sub>                      | $V_{DD} = 3.4 \text{ V}, V_{VM} = 0 \text{ V}$ | _                         | 1.5             | 4.0                        | μΑ        | 3               |  |

| Current consumption during overdischarge   IOPED   VDD = 1.5 V, VV |                                       | $V_{DD} = 1.5 \text{ V}, V_{VM} = 0 \text{ V}$ | _                         | ı               | 3.0                        | μΑ        | 3               |  |

| Output Resistance                                                  |                                       |                                                |                           |                 |                            |           |                 |  |

| CO pin resistance "H" 1                                            | R <sub>COH1</sub>                     | _                                              | 2.5                       | 10              | 30                         | kΩ        | 4               |  |

| CO pin resistance "L" 1                                            | R <sub>COL1</sub>                     | _                                              | 2.5                       | 10              | 30                         | kΩ        | 4               |  |

| DO pin resistance "H"                                              | R <sub>DOH</sub>                      | _                                              | 2.5                       | 10              | 30                         | kΩ        | 4               |  |

| DO pin resistance "L"                                              | R <sub>DOL</sub>                      | _                                              | 2.5                       | 10              | 30                         | kΩ        | 4               |  |

| CO pin resistance "H" 2                                            | R <sub>COH2</sub>                     | Active "L"                                     | 0.5                       | 4               | _                          | $M\Omega$ | 4               |  |

| CO pin resistance "L" 2                                            | R <sub>COL2</sub>                     | Active "H"                                     | 0.5                       | 4               | _                          | $M\Omega$ | 4               |  |

| Delay Time                                                         |                                       |                                                |                           |                 |                            |           |                 |  |

| Overcharge detection delay time                                    | tcu                                   | _                                              | $t_{\text{CU}}\times 0.5$ | tcu             | $t_{\text{CU}} \times 2.5$ | -         | 5               |  |

| Overcharge release delay time                                      | t <sub>CL</sub>                       | -                                              | $t_{\text{CL}}\times 0.5$ | t <sub>CL</sub> | $t_{\text{CL}} \times 2.5$ | -         | 5               |  |

| Overdischarge detection delay time                                 | $t_{DL}$                              | _                                              | $t_{\text{DL}}\times 0.5$ | $t_{DL}$        | $t_{\text{DL}} \times 2.5$ | -         | 5               |  |

<sup>\*1.</sup> Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

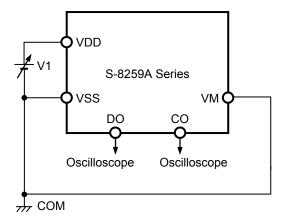

#### ■ Test Circuits

Caution Unless otherwise specified, the output voltage levels "H" and "L" at CO pin ( $V_{CO}$ ) are judged by  $V_{VM}$  + 1.0 V, and the output voltage levels "H" and "L" at DO pin ( $V_{DO}$ ) are judged by  $V_{SS}$  + 1.0 V. Judge the CO pin level with respect to  $V_{VM}$  and the DO pin level with respect to  $V_{SS}$ .

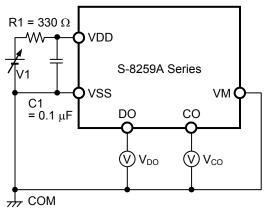

### Overcharge detection voltage, overcharge release voltage (Test circuit 1)

#### 1.1 Active "H"

Overcharge detection voltage ( $V_{CU}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "L" to "H" when the voltage V1 is gradually increased from the starting condition of V1 = 3.4 V. Overcharge release voltage ( $V_{CL}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "H" to "L" when the voltage V1 is then gradually decreased. Overcharge hysteresis voltage ( $V_{HC}$ ) is defined as the difference between  $V_{CU}$  and  $V_{CL}$ .

#### 1. 2 Active "L"

Overcharge detection voltage ( $V_{CU}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "H" to "L" when the voltage V1 is gradually increased from the starting condition of V1 = 3.4 V. Overcharge release voltage ( $V_{CL}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "L" to "H" when the voltage V1 is then gradually decreased. Overcharge hysteresis voltage ( $V_{HC}$ ) is defined as the difference between  $V_{CU}$  and  $V_{CL}$ .

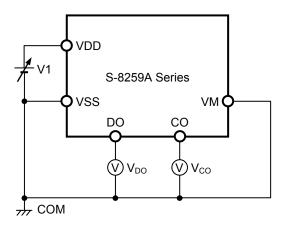

### Overdischarge detection voltage, overdischarge release voltage (Test circuit 2)

Overdischarge detection voltage ( $V_{DL}$ ) is defined as the voltage V1 at which  $V_{DO}$  goes from "H" to "L" when the voltage V1 is gradually decreased from the starting condition of V1 = 3.4 V. Overdischarge release voltage ( $V_{DU}$ ) is defined as the voltage V1 at which  $V_{DO}$  goes from "L" to "H" when the voltage V1 is then gradually increased. Overdischarge hysteresis voltage ( $V_{HD}$ ) is defined as the difference between  $V_{DU}$  and  $V_{DL}$ .

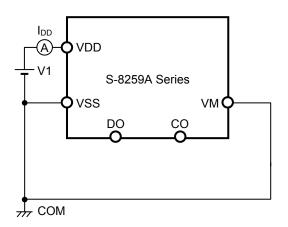

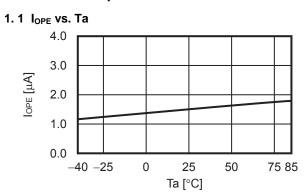

# 3. Current consumption during operation (Test circuit 3)

The current consumption during operation ( $I_{OPE}$ ) is the current that flows through VDD pin ( $I_{DD}$ ) under the set condition of V1 = 3.4 V.

# 4. Current consumption during overdischarge (Test circuit 3)

The current consumption during overdischarge ( $I_{OPED}$ ) is  $I_{DD}$  under the set condition of V1 = 1.5 V.

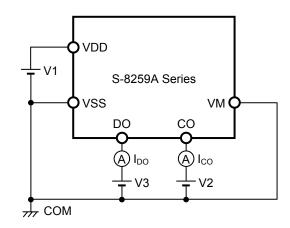

# 5. CO pin resistance "H" 1 (Test circuit 4)

### 5. 1 Active "H"

The CO pin resistance "H" 1 ( $R_{COH1}$ ) is the resistance between VDD pin and CO pin under the set conditions of V1 = 4.7 V, V2 = 4.3 V.

#### 5. 2 Active "L"

The CO pin resistance "H" 1 ( $R_{COH1}$ ) is the resistance between VDD pin and CO pin under the set conditions of V1 = 3.4 V, V2 = 3.0 V.

# 6. CO pin resistance "L" 1 (Test circuit 4)

#### C 4 Aathra || | | |

i Active ii

The CO pin resistance "L" 1 ( $R_{COL1}$ ) is the resistance between VM pin and CO pin under the set conditions of V1 = 3.4 V, V2 = 0.4 V.

#### 6. 2 Active "H"

The CO pin resistance "L" 1 ( $R_{COL1}$ ) is the resistance between VM pin and CO pin under the set conditions of V1 = 4.7 V, V2 = 0.4 V.

# 7. DO pin resistance "H" (Test circuit 4)

The DO pin resistance "H" ( $R_{DOH}$ ) is the resistance between VDD pin and DO pin under the set conditions of V1 = 3.4 V, V3 = 3.0 V.

## 8. DO pin resistance "L"

#### (Test circuit 4)

The DO pin resistance "L" ( $R_{DOL}$ ) is the resistance between VSS pin and DO pin under the set conditions of V1 = 1.8 V, V3 = 0.4 V.

### 9. CO pin resistance "H" 2 (Active "L")

#### (Test circuit 4)

The CO pin resistance "H" 2 ( $R_{COH2}$ ) is the resistance between VDD pin and CO pin under the set conditions of V1 = 4.7 V, V2 = 0 V.

### CO pin resistance "L" 2 (Active "H") (Test circuit 4)

The CO pin resistance "L" 2 ( $R_{COL2}$ ) is the resistance between VDD pin and CO pin under the set conditions of V1 = 4.7 V, V2 = 4.7 V.

## 11. Overcharge detection delay time

#### (Test circuit 5)

#### 11.1 Active "H"

The overcharge detection delay time ( $t_{CU}$ ) is the time needed for  $V_{CO}$  to go to "H" just after the voltage V1 increases and exceeds  $V_{CU}$  under the set condition of V1 = 3.4 V.

#### 11. 2 Active "L"

The overcharge detection delay time ( $t_{CU}$ ) is the time needed for  $V_{CO}$  to go to "L" just after the voltage V1 increases and exceeds  $V_{CU}$  under the set condition of V1 = 3.4 V.

# 12. Overcharge release delay time (Test circuit 5)

## 12. 1 Active "H"

The overcharge release delay time ( $t_{CL}$ ) is the time needed for  $V_{CO}$  to go to "L" just after the voltage V1 decreases and falls below  $V_{CL}$  under the set condition of V1 = 4.7 V.

#### 12. 2 Active "L"

The overcharge release delay time ( $t_{CL}$ ) is the time needed for  $V_{CO}$  to go to "H" just after the voltage V1 decreases and falls below  $V_{CL}$  under the set condition of V1 = 4.7 V.

# 13. Overdischarge detection delay time (Test circuit 5)

The overdischarge detection delay time ( $t_{DL}$ ) is the time needed for  $V_{DO}$  to go to "L" after the voltage V1 decreases and falls below  $V_{DL}$  under the set condition of V1 = 3.4 V.

Figure 5 Test Circuit 1

Figure 6 Test Circuit 2

Figure 7 Test Circuit 3

Figure 8 Test Circuit 4

Figure 9 Test Circuit 5

12 ABLIC Inc.

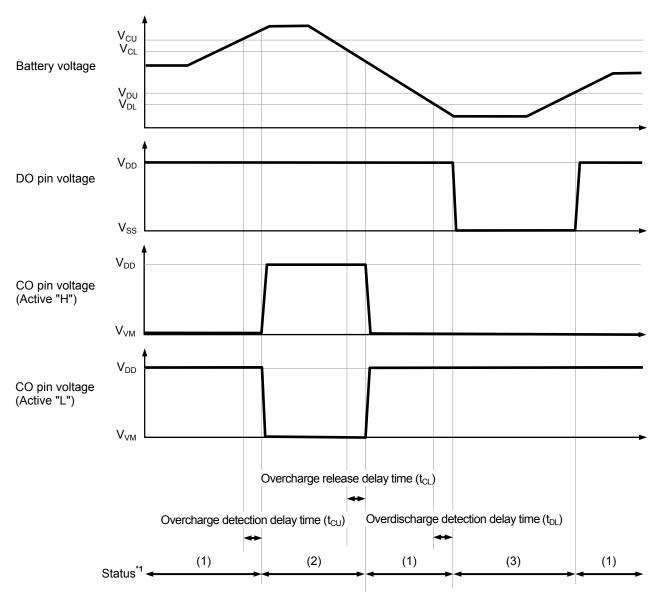

## ■ Operation

Remark Refer to "■ Connection Example".

#### 1. Normal status

The S-8259A Series monitors the voltage of the battery connected between VDD pin and VSS pin to control charging and discharging. When the battery voltage is in the range from overdischarge detection voltage ( $V_{DL}$ ) to overcharge detection voltage ( $V_{CU}$ ), CO pin and DO pin both output the release signals. This condition is called the normal status.

#### 2. Overcharge status

When the battery voltage becomes higher than  $V_{\text{CU}}$  during charging in the normal status and the condition continues for the overcharge detection delay time ( $t_{\text{CU}}$ ) or longer, CO pin outputs the overcharge detection signal. This condition is called the overcharge status.

When the battery voltage falls below the overcharge release voltage ( $V_{CL}$ ) and the condition continues for the overcharge release delay time ( $t_{CL}$ ) or longer, the S-8259A Series releases the overcharge status.

#### 3. Overdischarge status

When the battery voltage falls below  $V_{DL}$  during discharging in the normal status and the condition continues for the overdischarge detection delay time ( $t_{DL}$ ) or longer, DO pin outputs the overdischarge detection signal. This condition is called the overdischarge status.

When the battery voltage exceeds the overdischarge release voltage  $(V_{DU})$ , the S-8259A Series releases the overdischarge status.

## **■** Timing Chart

## 1. Overcharge detection, overdischarge detection

- \*1. (1): Normal status

- (2): Overcharge status

- (3): Overdischarge status

Figure 10

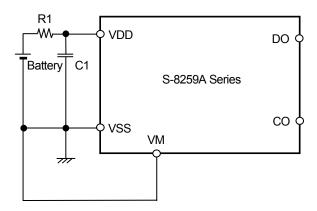

## **■** Connection Example

Figure 11

**Table 8 Constants for External Components**

| Symbol | Part      | Purpose                               | Min.     | Тур.   | Max.   | Remark |

|--------|-----------|---------------------------------------|----------|--------|--------|--------|

| R1     | Resistor  | ESD protection, For power fluctuation | 150 Ω    | 330 Ω  | 1 kΩ   | -      |

| C1     | Capacitor | For power fluctuation                 | 0.068 μF | 0.1 μF | 1.0 μF | _      |

Caution 1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

#### ■ Precautions

- The application conditions for the input voltage, output voltage, and load current should not exceed the package power dissipation.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any and all disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

## ■ Characteristics (Typical Data)

## 1. Current consumption

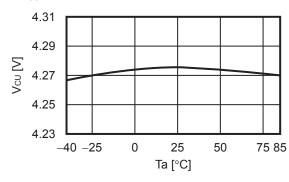

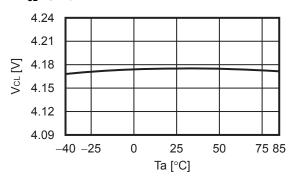

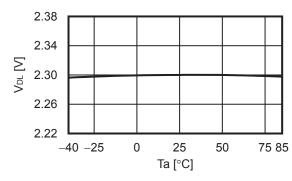

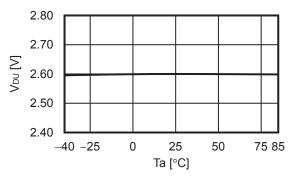

## 2. Detection voltage

#### 2. 1 V<sub>CU</sub> vs. Ta

## 2. 2 V<sub>CL</sub> vs. Ta

### 2. 3 V<sub>DL</sub> vs. Ta

2. 4 V<sub>DU</sub> vs. Ta

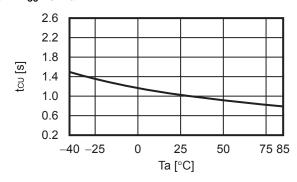

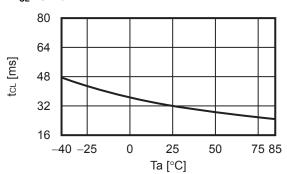

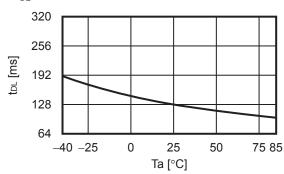

## 3. Delay time

3. 1 t<sub>CU</sub> vs. Ta

3. 2 t<sub>CL</sub> vs. Ta

3. 3  $\,t_{DL}$  vs. Ta

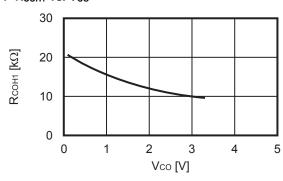

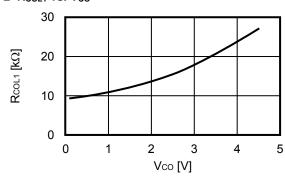

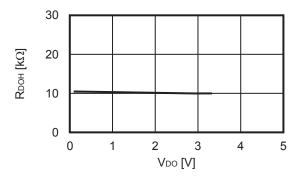

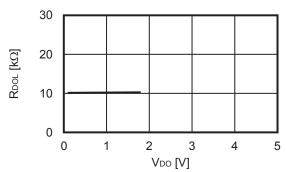

## 4. Output resistance

4.1 R<sub>COH1</sub> vs. V<sub>CO</sub>

4. 2 R<sub>COL1</sub> vs. V<sub>CO</sub>

4.3 RDOH vs. VDO

4.4 RDOL vs. VDO

## ■ Marking Specifications

## 1. SOT-23-6

(1) to (3): Product code (refer to **Product name vs. Product code**)

## No. MP006-A-P-SD-2.1

| TITLE      | SOT236-A-PKG Dimensions |  |  |  |

|------------|-------------------------|--|--|--|

| No.        | MP006-A-P-SD-2.1        |  |  |  |

| ANGLE      | <b>\$</b>               |  |  |  |

| UNIT       | mm                      |  |  |  |

|            |                         |  |  |  |

|            |                         |  |  |  |

|            |                         |  |  |  |

| ABLIC Inc. |                         |  |  |  |

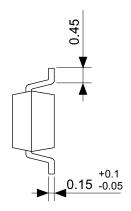

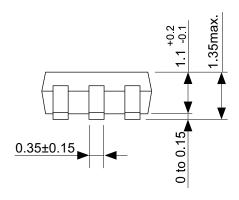

## No. MP006-A-C-SD-3.1

| TITLE      | SOT236-A-Carrier Tape |  |  |  |  |

|------------|-----------------------|--|--|--|--|

| No.        | MP006-A-C-SD-3.1      |  |  |  |  |

| ANGLE      |                       |  |  |  |  |

| UNIT       | mm                    |  |  |  |  |

|            |                       |  |  |  |  |

|            |                       |  |  |  |  |

|            |                       |  |  |  |  |

| ABLIC Inc. |                       |  |  |  |  |

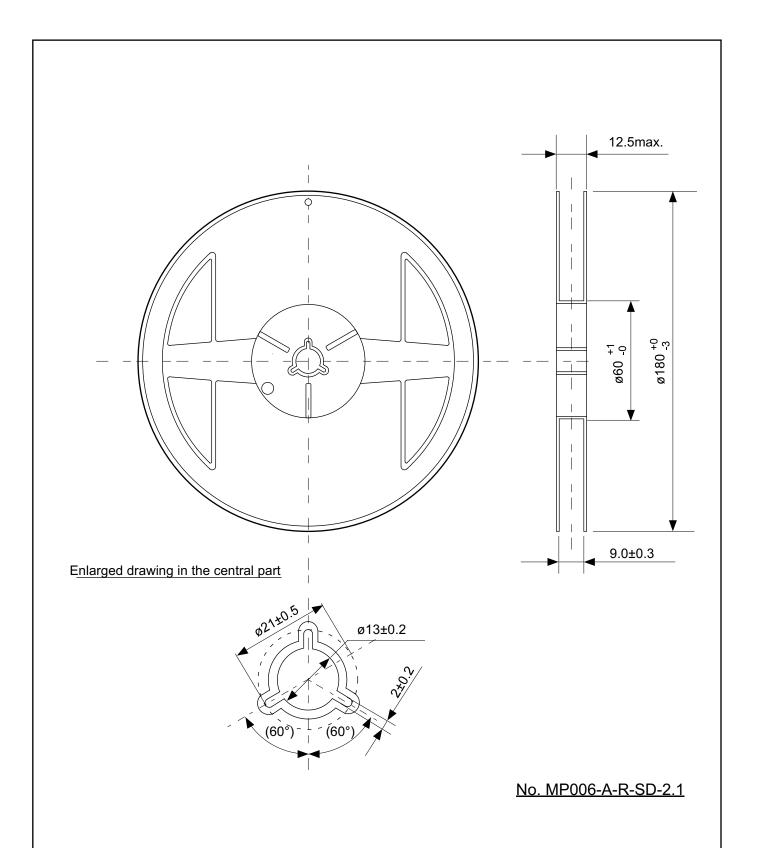

| TITLE      | SOT236-A-Reel    |  |  |  |  |

|------------|------------------|--|--|--|--|

| No.        | MP006-A-R-SD-2.1 |  |  |  |  |

| ANGLE      | QTY 3,000        |  |  |  |  |

| UNIT       | mm               |  |  |  |  |

|            |                  |  |  |  |  |

|            |                  |  |  |  |  |

|            |                  |  |  |  |  |

| ABLIC Inc. |                  |  |  |  |  |

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not responsible for damages caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not responsible for damages caused by the incorrect information described herein.

- 4. Be careful to use the products within their specified ranges. Pay special attention to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not responsible for damages caused by failures and / or accidents, etc. that occur due to the use of the products outside their specified ranges.

- 5. When using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products must not be used or provided (exported) for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not responsible for any provision (export) to those whose purpose is to develop, manufacture, use or store nuclear, biological or chemical weapons, missiles, or other military use.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses. Do not apply the products to the above listed devices and equipments without prior written permission by ABLIC Inc. Especially, the products cannot be used for life support devices, devices implanted in the human body and devices that directly affect human life, etc.

- Prior consultation with our sales office is required when considering the above uses.

- ABLIC Inc. is not responsible for damages caused by unauthorized or unspecified use of our products.

- 9. Semiconductor products may fail or malfunction with some probability.

- The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system must be sufficiently evaluated and applied on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc.

The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party without the express permission of ABLIC Inc. is strictly prohibited.

- 14. For more details on the information described herein, contact our sales office.

2.2-2018.06