# EL5100, EL5101, EL5300

200MHz Slew Enhanced VFA

FN7330 Rev 3.00 May 3, 2007

The EL5100, EL5101, and EL5300 represent high-speed voltage feedback amplifiers based on the current feedback amplifier architecture. This gives the typical high slew rate benefits of a CFA family along with the stability and ease of use associated with the VFA type architecture. This family is available in single, dual, and triple versions, with 200MHz, 400MHz, and 700MHz versions. This family operates on single 5V or ±5V supplies from minimum supply current. The EL5100 and EL5300 also feature an output enable function, which can be used to put the output in to a high-impedance mode. This enables the outputs of multiple amplifiers to be tied together for use in multiplexing applications.

### **Features**

- · Pb-free plus anneal available (RoHS compliant)

- · Specified for 5V or ±5V applications

- Power-down to 17µA/amplifier

- -3dB bandwidth = 200MHz

- ±0.1dB bandwidth = 20MHz

- · Low supply current = 2.5mA

- Slew rate = 2200V/µs

- Low offset voltage = 4mV max

- Output current = 100mA

- A<sub>VOL</sub> = 1000

- Diff gain/phase = 0.08%/0.1°

### **Applications**

- · Video amplifiers

- · PCMCIA applications

- · A/D drivers

- · Line drivers

- · Portable computers

- High speed communications

- · RGB applications

- · Broadcast equipment

- · Active filtering

## **Ordering Information**

| PART NUMBER          | PART<br>MARKING | TAPE AND REEL | PACKAGE                        | PKG.<br>DWG. # |

|----------------------|-----------------|---------------|--------------------------------|----------------|

| EL5100IS             | 5100IS          | -             | 8 Ld SOIC (150 mil)            | MDP0027        |

| EL5100IS-T7          | 5100IS          | 7"            | 8 Ld SOIC (150 mil)            | MDP0027        |

| EL5100IS-T13         | 5100IS          | 13"           | 8 Ld SOIC (150 mil)            | MDP0027        |

| EL5100ISZ (Note)     | 5100ISZ         | -             | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027        |

| EL5100ISZ-T7 (Note)  | 5100ISZ         | 7"            | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027        |

| EL5100ISZ-T13 (Note) | 5100ISZ         | 13"           | 8 Ld SOIC (150 mil) (Pb-free)  | MDP0027        |

| EL5100IW-T7          | у               | 7" (3k pcs)   | 6 Ld SOT-23                    | MDP0038        |

| EL5100IW-T7A         | у               | 7" (250 pcs)  | 6 Ld SOT-23                    | MDP0038        |

| EL5101IW-T7          | 2               | 7" (3k pcs)   | 5 Ld SOT-23                    | MDP0038        |

| EL5101IW-T7A         | 2               | 7" (250 pcs)  | 5 Ld SOT-23                    | MDP0038        |

| EL5300IU             | 5300IU          | -             | 16 Ld QSOP (150 mil)           | MDP0040        |

| EL5300IU-T7          | 5300IU          | 7"            | 16 Ld QSOP (150 mil)           | MDP0040        |

| EL5300IU-T13         | 5300IU          | 13"           | 16 Ld QSOP (150 mil)           | MDP0040        |

| EL5300IUZ (Note)     | 5300IUZ         | -             | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040        |

| EL5300IUZ-T7 (Note)  | 5300IUZ         | 7"            | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040        |

| EL5300IUZ-T13 (Note) | 5300IUZ         | 13"           | 16 Ld QSOP (150 mil) (Pb-free) | MDP0040        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

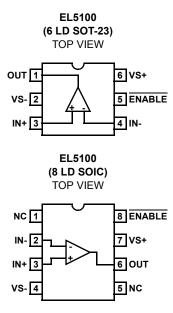

## **Pinouts**

###

Maximum Slewrate from  $V_S$ + to  $V_S$ - . . . . . . . . . . . . . . . .  $1V/\mu s$

### **Thermal Information**

| -65°C to +150°C |

|-----------------|

| 40°C to +85°C   |

| +150°C          |

| see link below  |

| )               |

|                 |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **DC Electrical Specifications** $V_S = \pm 5V$ , GND = 0V, $T_A = +25$ °C, $V_{CM} = 0V$ , $V_{OUT} = 0V$ , $V_{ENABLE} = GND$ or OPEN, Unless Otherwise Specified.

| PARAMETER          | DESCRIPTION                                   | CONDITIONS                                                | MIN                 | TYP  | MAX                 | UNIT  |

|--------------------|-----------------------------------------------|-----------------------------------------------------------|---------------------|------|---------------------|-------|

| V <sub>OS</sub>    | Offset Voltage                                |                                                           | -4                  | 1    | 4                   | mV    |

| TCV <sub>OS</sub>  | Offset Voltage Temperature Coefficient        | Measured from T <sub>MIN</sub> to T <sub>MAX</sub>        |                     | 8    |                     | μV/°C |

| IB                 | Input Bias Current                            | V <sub>IN</sub> = 0V                                      | -6                  | 2    | 6                   | μΑ    |

| Ios                | Input Offset Current                          | V <sub>IN</sub> = 0V                                      | -2.5                | 0.5  | 2.5                 | μΑ    |

| TCI <sub>OS</sub>  | Input Bias Current Temperature<br>Coefficient | Measured from T <sub>MIN</sub> to T <sub>MAX</sub>        |                     | 8    |                     | nA/°C |

| PSRR               | Power Supply Rejection Ratio                  |                                                           | 70                  | 90   |                     | dB    |

| CMRR               | Common Mode Rejection Ratio                   | V <sub>CM</sub> from -3V to +3V                           | 60                  | 75   |                     | dB    |

| CMIR               | Common Mode Input Range                       | Guaranteed by CMRR test                                   | -3                  |      | +3                  | ٧     |

| R <sub>IN</sub>    | Input Resistance                              | V <sub>IN</sub> = -3V to +3V                              | 0.7                 | 1.2  |                     | МΩ    |

| C <sub>IN</sub>    | Input Capacitance                             |                                                           |                     | 1    |                     | pF    |

| I <sub>S,ON</sub>  | Supply Current - Enabled                      | Per amplifier                                             | 2.1                 | 2.5  | 2.9                 | mA    |

| I <sub>S,OFF</sub> | Supply Current - Shut Down                    | V <sub>S</sub> +, per amplifier                           | -5                  | 0    | 5                   | μA    |

|                    |                                               | V <sub>S</sub> -, per amplifier                           | 5                   | 17   | 25                  | μΑ    |

| PSOR               | Power Supply Operating Range                  |                                                           | 3.3                 |      | 12                  | ٧     |

| AVOL               | Open Loop Gain                                | $R_L$ = 1k $\Omega$ to GND, $V_{OUT}$ from -2.5V to +2.5V | 55                  | 60   |                     | dB    |

| V <sub>OP</sub>    | Positive Output Voltage Swing                 | $R_L$ = 150 $\Omega$ to GND                               | 3.2                 | 3.4  |                     | ٧     |

|                    |                                               | $R_L$ = 1k $\Omega$ to GND                                | 3.6                 | 3.8  |                     | ٧     |

| V <sub>ON</sub>    | Negative Output Voltage Swing                 | $R_L$ = 150 $\Omega$ to GND                               |                     | -3.4 | -3.2                | ٧     |

|                    |                                               | $R_L$ = 1k $\Omega$ to GND                                |                     | -3.8 | -3.6                | V     |

| lout               | Output Current                                | R <sub>L</sub> = 10Ω to 0V                                | ±60                 | ±100 |                     | mA    |

| V <sub>IH-EN</sub> | ENABLE pin Voltage for Power Up               |                                                           | V <sub>S</sub> + -4 |      |                     | ٧     |

| V <sub>IL-EN</sub> | ENABLE pin Voltage for Shut Down              |                                                           |                     |      | V <sub>S</sub> + -1 | V     |

| I <sub>EN</sub>    | Enable Pin Current                            | Enabled, V <sub>EN</sub> = 0V                             | -1                  |      | 1                   | μA    |

|                    |                                               | Disabled, V <sub>EN</sub> = 5V                            | 5                   | 17   | 25                  | μA    |

Closed Loop AC Electrical Specifications  $V_S = \pm 5V$ ,  $T_A = 25^{\circ}C$ ,  $V_{ENABLE} = 0V$ ,  $A_V = +1$ ,  $R_F = 0\Omega$ ,  $R_L = 150\Omega$  to GND, unless otherwise specified.

| PARAMETER        | DESCRIPTION                                               | CONDITIONS                                                            | MIN  | TYP  | MAX  | UNIT   |

|------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|--------|

| BW               | -3dB Bandwidth (V <sub>OUT</sub> = 200mV <sub>P-P</sub> ) | $V_S = \pm 5V$ , $A_V = 1$ , $R_F = 0\Omega$                          | 150  | 200  |      | MHz    |

| SR               | Slew Rate                                                 | $R_L = 100\Omega$ , $V_{OUT} = -3V$ to +3V, $A_V = +2$                | 1500 | 2200 | 4500 | V/µs   |

| $t_{R},t_{F}$    | Rise Time, Fall Time                                      | ±0.1V step                                                            |      | 2.8  |      | ns     |

| os               | Overshoot                                                 | ±0.1V step                                                            |      | 10   |      | %      |

| t <sub>PD</sub>  | Propagation Delay                                         | ±0.1V step                                                            |      | 3.2  |      | ns     |

| t <sub>S</sub>   | 0.1% Settling Time                                        | $V_S = \pm 5V$ , $R_L = 500\Omega$ , $A_V = 1$ , $V_{OUT} = \pm 2.5V$ |      | 20   |      | ns     |

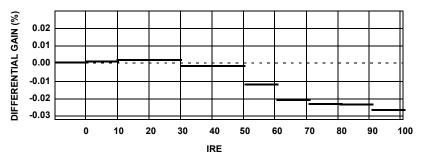

| dG               | Differential Gain                                         | $A_V = 2$ , $R_L = 150\Omega$ , $V_{INDC} = -1$ to +1V                |      | 0.08 |      | %      |

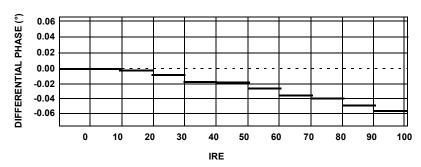

| dP               | Differential Phase                                        | $A_V = 2$ , $R_L = 150\Omega$ , $V_{INDC} = -1$ to +1V                |      | 0.1  |      | ٥      |

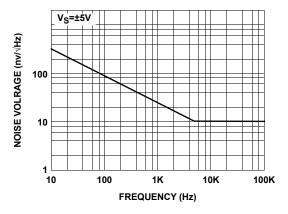

| e <sub>N</sub>   | Input Noise Voltage                                       | f = 10kHz                                                             |      | 10   |      | nV/√Hz |

| i <sub>N</sub>   | Input Noise Current                                       | f = 10kHz                                                             |      | 7    |      | pA/√Hz |

| t <sub>DIS</sub> | Disable Time                                              |                                                                       |      | 180  |      | ns     |

| t <sub>EN</sub>  | Enable Time                                               |                                                                       |      | 650  |      | ns     |

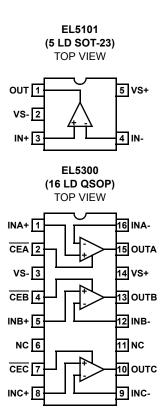

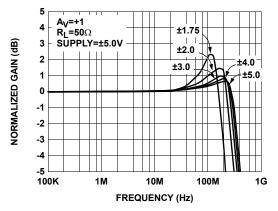

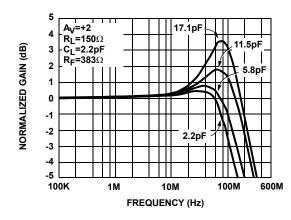

## **Typical Performance Curves**

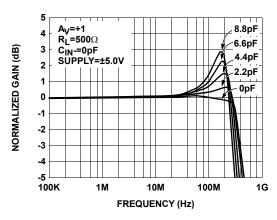

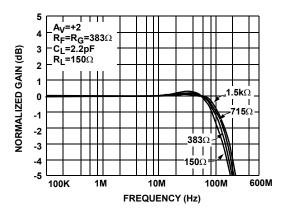

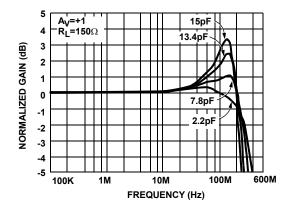

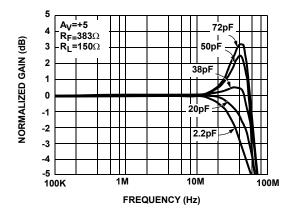

FIGURE 1. GAIN vs FREQUENCY FOR VARIOUS  $C_L$

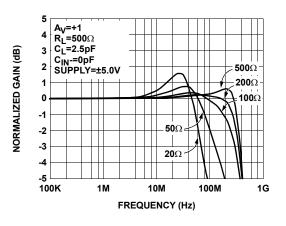

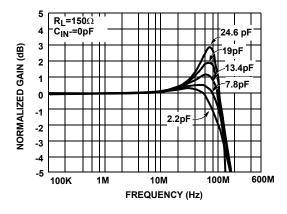

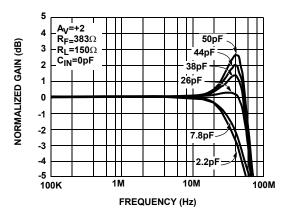

FIGURE 3. GAIN vs FREQUENCY FOR VARIOUS CIN-

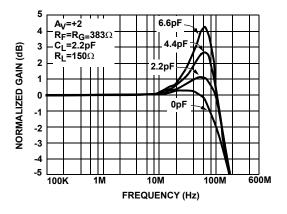

FIGURE 2. GAIN vs FREQUENCY FOR VARIOUS  $C_L$

FIGURE 4. GAIN vs FREQUENCY FOR VARIOUS CIN-

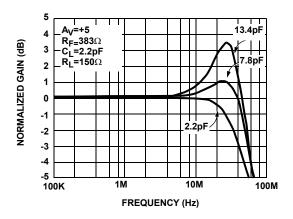

FIGURE 5. GAIN vs FREQUENCY FOR VARIOUS  $C_{IN}$  (-)

FIGURE 7. GAIN vs FREQUENCY FOR VARIOUS RL

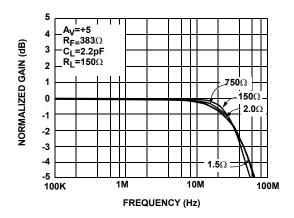

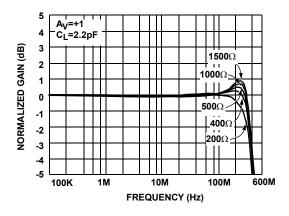

FIGURE 9. GAIN vs FREQUENCY FOR VARIOUS  $R_{\mathsf{L}}$

FIGURE 6. GAIN vs FREQUENCY FOR VARIOUS RL

FIGURE 8. GAIN vs FREQUENCY FOR VARIOUS RL

FIGURE 10. EQUIVALENT INPUT VOLTAGE NOISE vs **FREQUENCY**

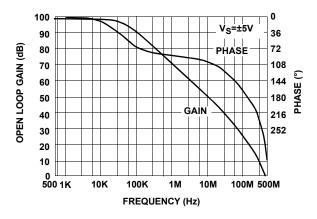

FIGURE 11. OPEN LOOP GAIN AND PHASE vs FREQUENCY

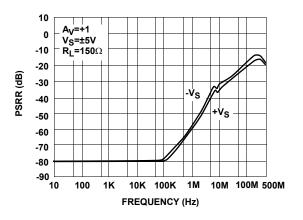

FIGURE 13. PSRR vs FREQUENCY

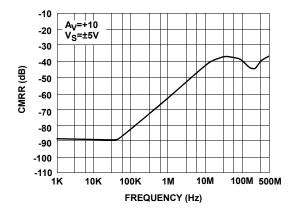

FIGURE 15. LARGE SIGNAL RISE TIME

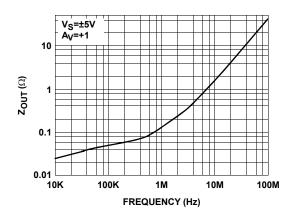

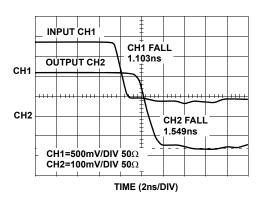

FIGURE 12. Z<sub>OUT</sub> vs FREQUENCY

FIGURE 14. CMRR vs FREQUENCY

FIGURE 16. LARGE SIGNAL FALL TIME

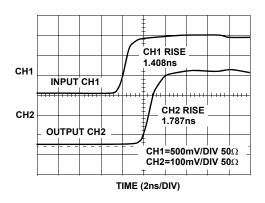

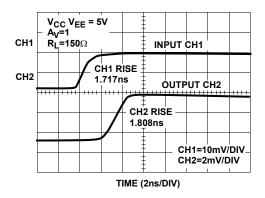

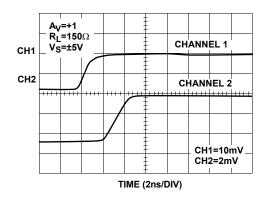

FIGURE 17. SMALL SIGNAL RISE TIME

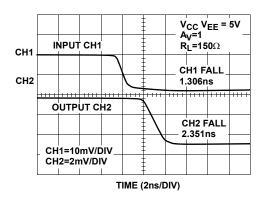

FIGURE 19. SMALL SIGNAL FALL TIME

FIGURE 21. GAIN vs FREQUENCY FOR VARIOUS CL

FIGURE 18. SMALL SIGNAL RISE TIME

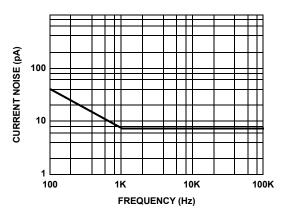

FIGURE 20. CURRENT NOISE

FIGURE 22. GAIN vs FREQUENCY FOR VARIOUS CL

FIGURE 23. GAIN vs FREQUENCY FOR VARIOUS CL

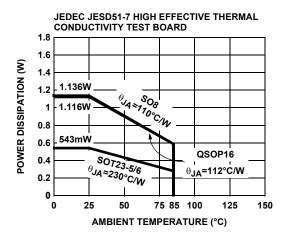

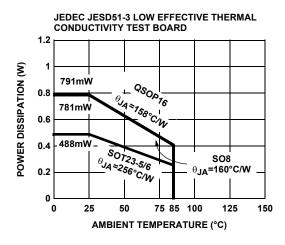

FIGURE 25. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

FIGURE 24. GAIN vs FREQUENCY FOR VARIOUS CL

FIGURE 26. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

FIGURE 27. DIFFERENTIAL GAIN (%)

FIGURE 28. DIFFERENTIAL PHASE (°)

## Application Information

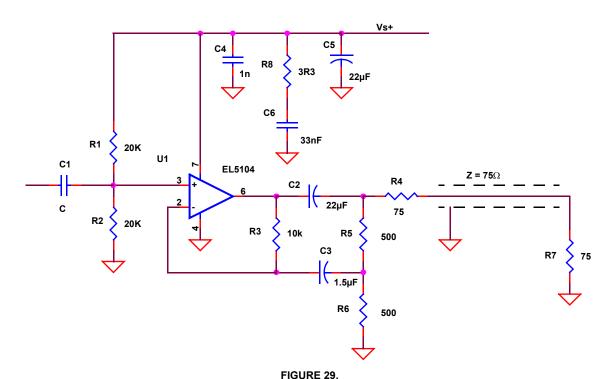

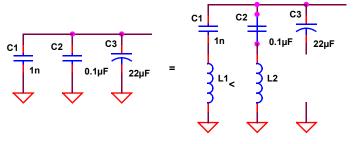

# Video Amplifier with Reduced Size Output Capacitance

If you have a video line driver  $Z = 75\Omega$ , the DC decoupling capacitor could be relatively large.

$$C = \frac{1}{2\pi \times R \times f} =$$

$$f = 10Hz, R = Z = 75\Omega, C = 132\mu F$$

By using the circuit below, C could be reduced to  $C2 = 22\mu F$ .

10

5

0

-5

-10

-15

-15

-10

-15

-20

-25

-30

-35

-40

-40

-45

1.00E+00 1.00E+02 1.00E+04 1.00E+06 1.00E+08 1.00E+01 1.00E+01 1.00E+09 FREQUENCY (Hz)

FIGURE 30. VIDEO-

The test result is shown on Figure 30.

By selecting a different value for C1, we could reduce the effect, created by C3 R3 and get flat response from 16Hz with an 1/5 value, price and size output capacitor. There is another, very important issue by using high bandwidth amplifiers.

In the past when the bandwidth of the operational amplifier ended at a few hundred kHz even at few MHz, the power-supply bypass was not a very critical issue, since a  $0.1\mu F$  capacitor "did the job", but today's amplifiers could have bandwidth, what used to be reserved for microwave circuits not to long time ago.

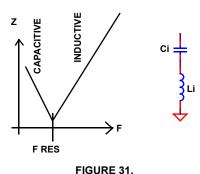

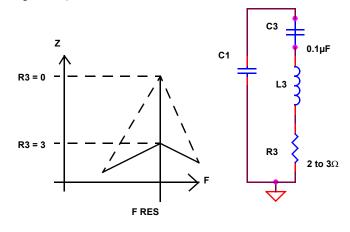

Therefore that high bandwidth amplifiers require the same respect what we reserve for microwave circuits. Particularly the power supply bypass and the pcb-layout could very heavily influence the performance of a modern high bandwidth amplifiers. It could happen above a few MHz, but it will happen above 100MHz, that the capacitor will behave like an inductor.

The reason for that is the very small but not zero value serial inductance of the capacitor.

The capacitor will behave as a capacitor up to its resonance frequency, above the resonance frequency it will behave as an inductor.

Just 1nHy inductance serial with 1nF capacitance will have serial resonance at:

$$F = \frac{1}{2\pi\sqrt{L\times C}}$$

C = 1nF, L = 1nHy, F = 159 MHz

And an other 1nHy is very easy to get together with the inductance of traces on the pcb, and therefore you could encounter resonances from ca 50MHz and above anywhere. So if the amplifier has a bandwidth of a few hundred MHz, the proper power supply by-pass could become a serious if not difficult task.

Intuitively, you would use capacitors value  $0.1\mu F$  parallel with a few  $\mu F$  tantalum, and to cure the effect of it's serial resonance put a smaller one parallel to it.

The result will surprise to you, because you will get even something worse than without the small capacitor.

What is happening there? Just look what we get:

FIGURE 32.

Above its serial resonance C2\* the ideal capacitance of C2 is a short, the Tantalum capacitor for high frequencies is not effective, the left over is C1 capacitor and L1 + L2 inductors, we get a parallel tank circuit, which is at it's resonance a high impedance path and do not carry any high frequency current, it does not work as bypass at all!

The impedance of a parallel tank circuit at resonance is dependent from it's Q. High Q high impedance.

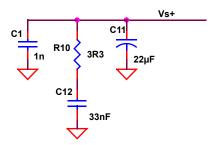

The Q of a parallel tank circuit could be reduced by bypassing it with a resistor, or adding a resistor in serial to one of the reactive components. Since the bypassing would short the DC supply we do have to go to add resistor in serial to the reactive component, we will ad a resistor serial with the inductor. (See Figure 33.)

FIGURE 33.

The final power supply bypass circuit will look:

FIGURE 34.

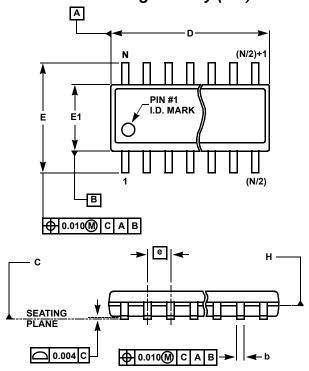

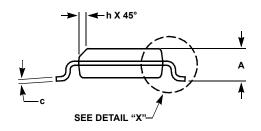

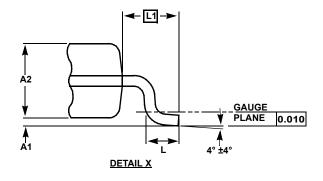

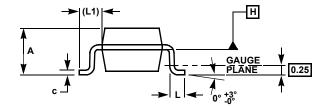

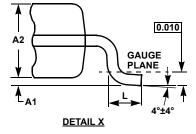

# Small Outline Package Family (SO)

## **MDP0027**

### **SMALL OUTLINE PACKAGE FAMILY (SO)**

|        | INCHES |       |                  |                           |                  |                  |                  |           |       |

|--------|--------|-------|------------------|---------------------------|------------------|------------------|------------------|-----------|-------|

| SYMBOL | SO-8   | SO-14 | SO16<br>(0.150") | SO16 (0.300")<br>(SOL-16) | SO20<br>(SOL-20) | SO24<br>(SOL-24) | SO28<br>(SOL-28) | TOLERANCE | NOTES |

| Α      | 0.068  | 0.068 | 0.068            | 0.104                     | 0.104            | 0.104            | 0.104            | MAX       | -     |

| A1     | 0.006  | 0.006 | 0.006            | 0.007                     | 0.007            | 0.007            | 0.007            | ±0.003    | -     |

| A2     | 0.057  | 0.057 | 0.057            | 0.092                     | 0.092            | 0.092            | 0.092            | ±0.002    | -     |

| b      | 0.017  | 0.017 | 0.017            | 0.017                     | 0.017            | 0.017            | 0.017            | ±0.003    | -     |

| С      | 0.009  | 0.009 | 0.009            | 0.011                     | 0.011            | 0.011            | 0.011            | ±0.001    | -     |

| D      | 0.193  | 0.341 | 0.390            | 0.406                     | 0.504            | 0.606            | 0.704            | ±0.004    | 1, 3  |

| Е      | 0.236  | 0.236 | 0.236            | 0.406                     | 0.406            | 0.406            | 0.406            | ±0.008    | -     |

| E1     | 0.154  | 0.154 | 0.154            | 0.295                     | 0.295            | 0.295            | 0.295            | ±0.004    | 2, 3  |

| е      | 0.050  | 0.050 | 0.050            | 0.050                     | 0.050            | 0.050            | 0.050            | Basic     | -     |

| L      | 0.025  | 0.025 | 0.025            | 0.030                     | 0.030            | 0.030            | 0.030            | ±0.009    | -     |

| L1     | 0.041  | 0.041 | 0.041            | 0.056                     | 0.056            | 0.056            | 0.056            | Basic     | -     |

| h      | 0.013  | 0.013 | 0.013            | 0.020                     | 0.020            | 0.020            | 0.020            | Reference | -     |

| N      | 8      | 14    | 16               | 16                        | 20               | 24               | 28               | Reference | -     |

NOTES:

Rev. M 2/07

- 1. Plastic or metal protrusions of 0.006" maximum per side are not included.

- 2. Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994

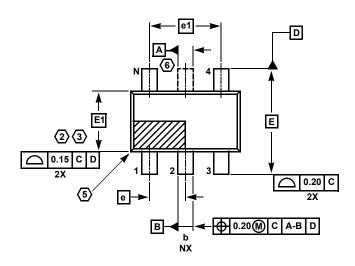

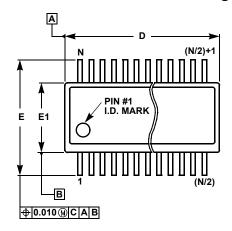

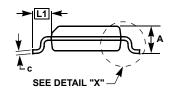

# SOT-23 Package Family

### **MDP0038**

### **SOT-23 PACKAGE FAMILY**

|        | MILLIN  |         |           |

|--------|---------|---------|-----------|

| SYMBOL | SOT23-5 | SOT23-6 | TOLERANCE |

| Α      | 1.45    | 1.45    | MAX       |

| A1     | 0.10    | 0.10    | ±0.05     |

| A2     | 1.14    | 1.14    | ±0.15     |

| b      | 0.40    | 0.40    | ±0.05     |

| С      | 0.14    | 0.14    | ±0.06     |

| D      | 2.90    | 2.90    | Basic     |

| E      | 2.80    | 2.80    | Basic     |

| E1     | 1.60    | 1.60    | Basic     |

| е      | 0.95    | 0.95    | Basic     |

| e1     | 1.90    | 1.90    | Basic     |

| L      | 0.45    | 0.45    | ±0.10     |

| L1     | 0.60    | 0.60    | Reference |

| N      | 5       | 6       | Reference |

Rev. F 2/07

### NOTES:

- 1. Plastic or metal protrusions of 0.25mm maximum per side are not included.

- Plastic interlead protrusions of 0.25mm maximum per side are not included.

- 3. This dimension is measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Index area Pin #1 I.D. will be located within the indicated zone (SOT23-6 only).

- 6. SOT23-5 version has no center lead (shown as a dashed line).

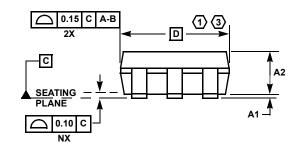

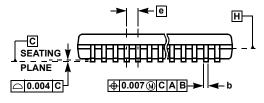

# Quarter Size Outline Plastic Packages Family (QSOP)

#### MDP0040

### QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        | INCHES |        |        |           |       |

|--------|--------|--------|--------|-----------|-------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |

| Α      | 0.068  | 0.068  | 0.068  | Max.      | -     |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -     |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -     |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -     |

| С      | 0.008  | 0.008  | 0.008  | ±0.001    | -     |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -     |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -     |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -     |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -     |

| N      | 16     | 24     | 28     | Reference | -     |

Rev. F 2/07

#### NOTES:

- Plastic or metal protrusions of 0.006" maximum per side are not included.

- Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

© Copyright Intersil Americas LLC 2004-2007. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>