## **BBT3420**

Quad 2.488-3.1875Gbps/Channel Transceiver

FN7481 Rev 1.00 September 14, 2005

## 1 Features

- Four channels of transmitter and receiver with serial data transfer rates of 2.488-3.1875Gbps/channel with full rate and half-rate operations

- Up to 12.75Gbps data rate at full duplex

- User-controlled dual-speed operation (per channel) 2.488-3.1875Gbps or 1.244-1.59Gbps

- IEEE 802.3ae-2002 10 GE and 10 GFC compliant

- XAUI, XGMII, and MDC/MDIO interfaces

- · XGMII format 10-bit parallel input/output data

- Supports HSTL 1.8V and 2.5V SSTL\_2

- Extensive configuration via 802.3-compliant MDC/MDIO serial interface

- 8bit/10bit Encoding/Decoding per channel with selectable parallel input/output data sizes

- Support optional 8b/10b encoder/decoder bypass operation

- · Integrated Equalization and Pre-emphasis

- · De-skewing and channel-to-channel alignment options

- · Low power, 250mW per channel typical

- · Meets jitter requirements with significant margin

- · Comma detection and synchronization, byte alignment

- Tx/Rx rate matching via IDLE insertion/deletion

- Receive signal detect and 16 levels of transmission medium equalization

- · CML transmit outputs with four levels of pre-emphasis

- Loopback

- Per-channel serial Tx-to-Rx and Rx-to-Tx parallel internal loopback modes

- · Single-ended/differential input Reference clock

- Double Data-Rate (DDR) mode, also optional SDR (Single Data Rate) on transmitter

- Support both source-centered and source-simultaneous clocking

- Long Run Length (512 bit) frequency lock ideal for proprietary encoding schemes Transmit byte clock schemes

- One Transmit Byte Clock (TBC) for each channel, or one TBC for all four channels

- · Received clock schemes

- Receive data aligned to local reference clock, to recovered clock for each channel, or to recovered clock for Channel A only

- · Supports Built-In Self Test (BIST) and IEEE 1149.1 JTAG

- On-chip 25Ω series output terminations (XGMII side)

- Standard 0.18µm 1.8V CMOS technology

- · 3.3V tolerant I/O

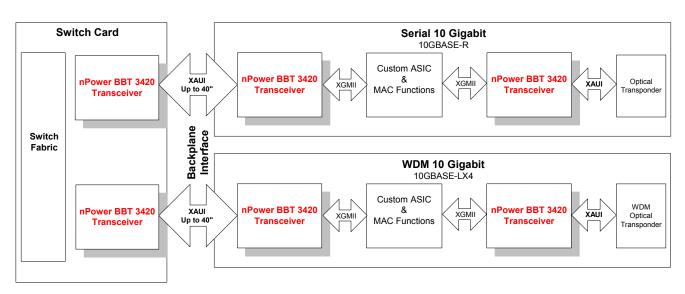

FIGURE 1-1. EXAMPLE BACKPLANE AND LINE CARD APPLICATIONS

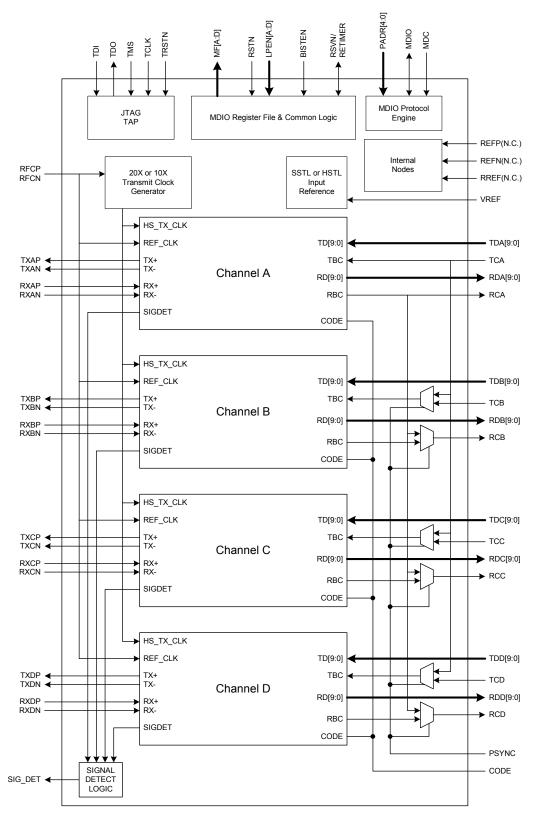

FIGURE 1-2. BBT3420 BLOCK DIAGRAM

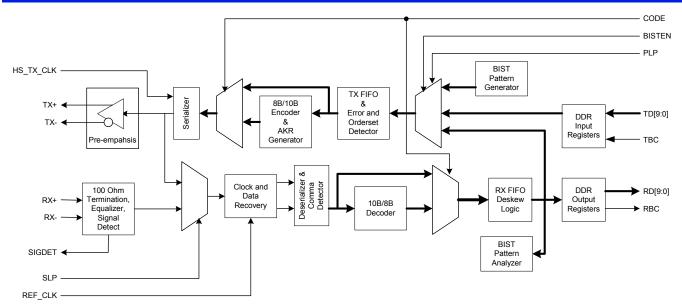

FIGURE 1-3. FUNCTIONAL BLOCK DIAGRAM OF A SINGLE CHANNEL

# 2 General Description

The BBT3420 is a quad 8-bit/10-bit parallel-to-serial and serial-to-parallel transceiver device ideal for high-bandwidth interconnection between line cards, serial backplanes, or optical modules, over interconnect media such as Printed Circuit Board (PCB) FR-4 traces or copper cables.

Each independent transceiver channel in BBT3420 is capable of operating at 2.488-3.1875Gbps at full-rate, and 1.244-1.59375Gbps at half-rate. The four on-chip transceivers shown in Figure 1-2 can also be configured as a single 10 Gigabit Attachment Unit Interface (XAUI), for both 10G Ethernet and 10G Fiber Channel or proprietary backplane interfaces, providing up to 12.75Gbps of data throughput at full duplex. The BBT3420 also supports the 10 Gigabit Media Independent Interface (XGMII) on the parallel interfaces. The device can be used as an XGMII Extended Sublayer (XGXS) device to support longer PCB traces between optical transceiver modules and switch fabrics, as shown in Figure 1-1.

As shown in Figure 1-3, each transceiver channel in BBT3420 contains a serializer, a deserializer, an 8b/10b encoder and decoder, as well as elastic buffers that provide the interface for serial data transmission and data recovery. Both the receive equalization and the transmit pre-emphasis are provided on each of the channels to maximize performance. In addition, a programmable receive FIFO in each channel aligns all incoming serial data to the local clock domain, adding or removing IDLE sequences as needed. This in return will eliminate the need for multiple clock domains for the interfaced ASIC device to the transceiver.

Each transceiver channel can also be configured to operate as a non-encoded 10-bit transceiver, allowing long strings of consecutive 1's or 0's (up to 512 bits). This feature enables the BBT3420 to accommodate proprietary encoded data links.

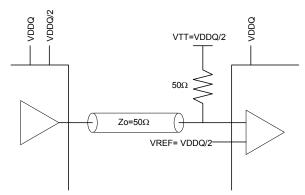

On each channel, the transmitter accepts up to 10-bit wide parallel SSTL\_2 or HSTL Class I/O (Figure 2-1) data, which is then serialized into high-speed NRZ (Non-Return to Zero) serial streams. The effective serial output impedance is nominally  $150\Omega$  differential.

The BBT3420 transceiver can be configured via pins and through the Management Data Input/Output (MDIO) interface specified in IEEE 802.3 Clause 22 or Clause 45. The device supports both the 5-bit PHY address for Clause 22 and the 5-bit port address for Clause 45. The four device addresses for Clause 45 are user selectable. The device also supports the Built-in Self Test (BIST) and IEEE 1149.1 (JTAG) for self-test purposes including serial and parallel loopback under either external pin or MDIO control, and Pseudo Random Bit Sequence (PRBS) generation and verification.

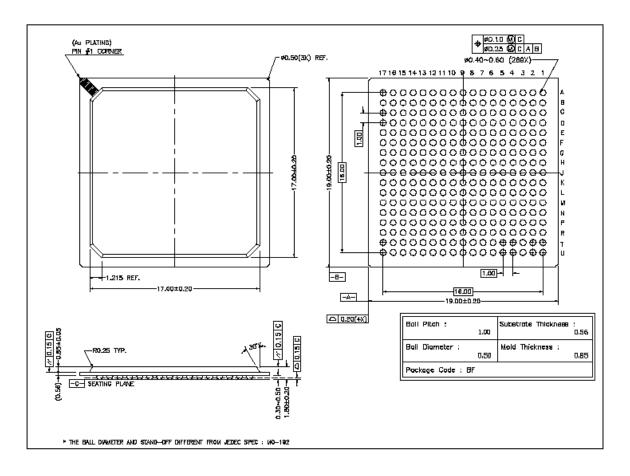

The BBT3420 is assembled in a 289-pin 19mm x 19mm HSBGA package. The device can operate with a single 1.8V supply and dissipates only 250mW per channel.

FIGURE 2-1. SSTL\_2/HSTL CLASS I I/O

## 3.0 Detailed Functional Description

## 3.1 Transmit Parallel Input Modes

The parallel side of each of the channels in BBT3420 may operate in either a 10-bit mode or a XGMII 9-bit mode. The parallel input mode selection is controlled by the CODE pin (Table 4-6) and the CODECENA bit in the MDIO register at address 11'h in Clause 22 format (Table 3-16) and/or C000'h in Clause 45 format (Table 3-32). In order to program the device for XGMII 9-bit mode, the CODE pin should be set HIGH and the CODECENA bit set to 1'b. For the 10-bit Mode setting, either the CODE pin should be set to LOW or the CODECENA bit should be set to 0'b.

#### 3.1.1 10-BIT MODE

In the 10-bit mode the 8b/10b Codec is disabled, and the externally encoded data are latched in the DDR input registers in increments of 10 bits. In this case, the user is responsible for generating and applying the proper input in the form of ordered sets, data, and correct 'comma' group signals, to ensure data coherence. The LSB (TDX[0]) is shifted out first on the serial side, and the MSB (TDX[9]) is shifted out last.

## 3.1.2 XGMII 9-BIT (8 BITS PLUS K CONTROL BIT) MODE

In the XGMII 9-bit mode, the unencoded data are latched in the DDR input registers in 9 bits at a time. The lower 8 bits (TD[A..D][7:0]) are byte-wide data or control values, and the 9<sup>th</sup> bit (TD[A..D][8]) is the "K" bit used to select special control characters for link management. In this mode, the 10<sup>th</sup> bit (TD[A..D][9]) is used for disparity error or code violation. The 8b/10b Codec is enabled, and converts the data and the valid control values.

The XGMII IDLE Code Register (Clause 22 Address 1B'h or Clause 45 Address C003'h) controls the data pattern that

represents an IDLE character. The default value of this register is 07'h. The register can be programmed to any 8-bit value excluding the already defined (control) values shown in Table 3-1.

When both the TRANS\_EN bit (Clause 22 Address 10'h in Table 3-15 or Clause 45 Address C001'h in Table 3-33) and the AKR\_EN bit (Clause 22 Address 1D'h in Table 3-28 or Clause 45 Address C001'h in Table 3-33) are set to 1, or when the XAUI\_EN bit is set, the IDLE character data pattern will be sequenced into /A/, /K/, and /R/ codes (IEEE 802.3ae-2002 specified). Alternatively, if neither of the AKR\_EN or XAUI\_EN bits are set, the XGMII IDLE and the /K/ code will both be transmitted as the XAUI /K/ code, and the /A/ and /R/ control codes will be transmitted as XAUI /A/ and /R/ codes respectively. The 8b/10b encoding patterns are described in Table 3-1. For valid operation, the XGMII and XAUI Lane 0 signals should be connected to the BBT3420 Channel A pins.

When the XAUI\_EN bit is set to 1, if a local/remote fault is received on the XAUI inputs, it will be passed as ||LF|| or ||RF|| Sequence Ordered\_sets respectively, i.e., /K28.4/D0.0/D0.0/D1.0(D2.0)/. Local fault is declared when any of the following conditions are detected:

- 1. No signal is detected in any one of four channels.

- No valid comma is detected in any one or more of the four channels.

- 3. When all the channels are not deskewed.

When the XAUI\_EN bit is set to 1, if a local/remote fault K28.4/D0.0/D0.0/D1.0(D2.0)/ is written to the XGMII transmit interface for XAUI transmission, the ||LF|| or ||RF|| Sequence Ordered\_set is transmitted according to the IEEE 802.3ae-2002 randomizing algorithm. Any other Sequence Ordered\_set will also be transmitted in the same way.

TABLE 3-1. VALID 8B/10B ENCODER PATTERNS

| K-BIT | TD DATA                 | TRANS_EN<br>BIT (Note 1) | AKR_EN BIT<br>(Note 1) | SERIAL SERIAL CHARACTER CODE |        | NOTES and DESCRIPTION          |  |

|-------|-------------------------|--------------------------|------------------------|------------------------------|--------|--------------------------------|--|

| 0     | 0-FF'h                  | Х                        | Х                      | See 802.3-2002 Tab           | le36-1 | Valid Data Value               |  |

| 1     | = XGMII IDLE reg.       | 0                        | Х                      | Invalid code                 |        |                                |  |

|       | (Note 2) (default 07'h) | 1                        | 0                      | /K/                          | K28.5  | Comma (Sync)                   |  |

|       |                         |                          | 1                      | /A/ /K/ /R/                  |        | IEEE802.3ae 48.2.4.2 algorithm |  |

| 1     | BC                      | Х                        | 0                      | /K/                          | K28.5  | Comma (Sync)                   |  |

|       |                         |                          | 1                      | /A/ /K/ /R/                  | 1      | IEEE802.3ae 48.2.4.2 algorithm |  |

| 1     | 7C                      | Х                        | 0                      | /A/                          | K28.3  | Align                          |  |

|       |                         |                          | 1                      | /A/ /K/ /R/                  | 1      | IEEE802.3ae 48.2.4.2 algorithm |  |

| 1     | 1C                      | Х                        | 0                      | /R/                          | K28.0  | Alternate Idle (Skip)          |  |

|       |                         |                          | 1                      | /A/ /K/ /R/                  |        | IEEE802.3ae 48.2.4.2 algorithm |  |

| 1     | FB                      | Х                        | Х                      | /S/                          | K27.7  | Start                          |  |

| 1     | FD                      | Х                        | Х                      | /T/                          | K29.7  | Terminate                      |  |

TABLE 3-1. VALID 8B/10B ENCODER PATTERNS (Continued)

| K-BIT | TD DATA      | TRANS_EN<br>BIT (Note 1) | AKR_EN BIT<br>(Note 1) | SERIAL<br>CHARACTER | SERIAL<br>CODE | NOTES and DESCRIPTION       |

|-------|--------------|--------------------------|------------------------|---------------------|----------------|-----------------------------|

| 1     | 3C           | Х                        | Х                      |                     | K28.1          | Extra comma                 |

| 1     | 5C           | Х                        | Х                      | /F/                 | K28.2          | Signal Ordered_Set marker   |

| 1     | 9C           | Х                        | Х                      | /Q/                 | K28.4          | Sequence Ordered_Set marker |

| 1     | DC           | Х                        | Х                      |                     | K28.6          |                             |

| 1     | FC           | Х                        | Х                      |                     | K28.7          | Repeat gives False Comma    |

| 1     | F7           | Х                        | Х                      |                     | K23.7          |                             |

| 1     | FE           | Х                        | Х                      | /E/                 | K30.7          | Error Code                  |

| 1     | (all others) | Х                        | Х                      | Invalid code        |                | Error Code                  |

#### NOTES:

- 1. If the XAUI\_EN bit is set, the BBT3420 acts as though both the TRANS\_EN and AKR\_EN bits are set.

- 2. The XGMII IDLE character is set by the XGMII IDLE register, address 1B'h/C003'h (see Table 3-26), default value 07'h, combined with the K bit (XGMII value 107'h).

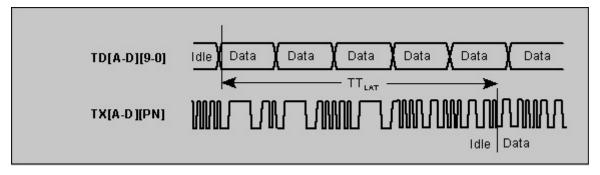

## 3.2 Transmit Byte Clock

#### 3.2.1 FULL- AND HALF-RATE MODE

Since the BBT3420 normally employs Double Data Rate (DDR) timing, the local reference clock requirement is lowered to 124.4-159.375MHz. The Transmit Byte Clock (TBC) must be frequency-synchronous with the local reference clock. For any channel set to Half-Rate Clock Mode by the MDIO/MDC register 1F'h (for Clause 22) and/or C008'h (for Clause 45), see Table 3-30, the TBC must be provided at half the ref clock frequency, unless the TX\_SDR bit is set in the MDIO register C001'h (Clause 45, Table 3-33) and/or 1D'h (Clause 22, Table 3-28).

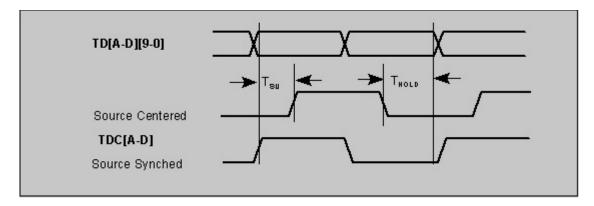

#### 3.2.2 SOURCE-CENTERED AND -SIMULTANEOUS MODE

For ease of ASIC timing, the BBT3420 provides the option for the TBC to be source-simultaneous or source-centered. In source-simultaneous mode, the ASIC is not required to adjust the TBC signal to the center of the data window. The internal latch clock of the BBT3420 is set to +5 serial bit times after the rising edge of the clock (TBC or RefClock) when the chip is reset. In source-centered mode, the BBT3420 expects stable data, with proper setup/hold time with respect to the TBC from the ASIC. The specific clocking mode is selectable by the MDIO/MDC register bit SC\_TBC at address 11'h in Clause 22 format, Table 3-16, and/or C001'h in Clause 45 format, Table 3-33.

## 3.2.3 TRUNKING MODE

The TBC source for each channel is determined by the trunking mode setting of the PSYNC pin. When trunking is turned on (PSYNC high), all four channels are latched by the Channel A TBC on pin TCA. In non-trunking mode, each channel is latched with its corresponding TBC pin TC[A-D] independently. Note that PSYNC will also force trunking of the Receive Byte Clocks (see below). Alternatively, the TC[A-D]

inputs may be driven from a common source, such as the local reference clock.

#### 3.3 Transmit FIFO

A 4-byte-deep input FIFO is used to accommodate any TBC or data drift. The initial pointer value is 2 bytes, which can accommodate ±2 byte skew between channels, as well as drift between the TBC and the reference clock. When the FIFO depth is at one, the transmit data is ready for output on the next TXC.

#### 3.4 Serializer

The serializer accepts 10-bit transmission characters and converts them from a parallel format to a serial bit stream at 2.488-3.1875Gbps. The system designer is expected to treat such signals on the PCB as transmission lines and to use a controlled impedance and suitable termination.

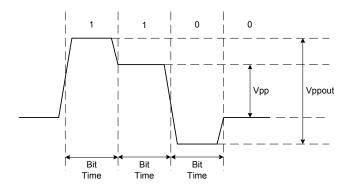

## 3.5 Pre-emphasis

In order to compensate for the loss of the high-frequency signal components through PCB or cable, four levels of programmable pre-emphasis have been added to all serial transmit channels. This maximizes the data eye opening at the receiver inputs and enhances the bit error rate performance of the system. The MDIO Register at Address 1C'h (for Clause 22) and/or C005'h (for Clause 45) (see Table 3-27) controls the level of pre-emphasis. Note that the formula used to determine the pre-emphasis valuse is NOT the same as that used in the IEEE 802.3ak-2004 specification for this parameter.

**TABLE 3-2. PRE-EMPHASIS CONTROL**

| CLAUSE 22<br>ADDRESS 1C'h OR<br>CLAUSE 45<br>ADDRESS C005'h<br>BIT 15 | CLAUSE 22<br>ADDRESS 1C'h OR<br>CLAUSE 45<br>ADDRESS C005'h<br>BIT 14 | PRE-EMPHASIS<br>VALUE =<br>(V <sub>PPOUT</sub> /V <sub>PP</sub> )-1 |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|

| 0                                                                     | 0                                                                     | No Pre-Emphasis                                                     |

| 0                                                                     | 1                                                                     | 0.18                                                                |

| 1                                                                     | 0                                                                     | 0.38                                                                |

| 1                                                                     | 1                                                                     | 0.75                                                                |

FIGURE 3-1. PRE-EMPHASIS OUTPUT ILLUSTRATION

## 3.6 Output Select - Serial Loopback

In normal mode, the serialized transmission TD[A..D][9..0] data will be placed on TX[A..D]P/N. When serial loopback is activated, Tx[AÖD] is internally looped back to Rx[AÖD] respectively.

#### 3.7 Receiver

The receiver detects and recovers the serial clock and data from the received data stream. After acquiring bit synchronization, the BBT3420 normally searches the serial bit stream for the occurrence of a comma character to obtain byte synchronization (byte alignment). The receiver then performs channel alignment and clock compensation, as desired. These are each discussed in the sections below.

# 3.7.1 Input Equalization and Transmission Line Termination

An equalizer has been added to each receiver input buffer, which boosts high-frequency edge response. The boost factor can be selected from 0 to F'h through MDIO. The MDIO register at address 1C'h (Clause 22), and/or C005'h (Clause 45), see Table 3-27, controls the boost value of the equalizer functions. A nominal  $100\Omega$  on-chip transmission-line termination resistor is integrated with the input equalizer, eliminating the requirement of an external termination resistor. This greatly improves the effectiveness of the termination, providing the best possible signal integrity.

## 3.7.2 Loss of Signal (LOS)

Loss of signal is an indication of gross signal error conditions. It is not an indication of signal coding health. It may be caused by poor connections, insufficient voltage swings, or out-ofrange signal frequency. If any of these conditions occurs, the SIG DET pin will be de-asserted. In addition, the MDIO MF\_CTRL register bits (Address 10'h for Clause 22 format, Table 3-15, and/or C001'h for Clause 45 format, Table 3-33) can be set to have the MF[A-D] pins provide per-channel indication of Loss of Signal conditions, the threshold being set by the MDIO LOS CONTROL register bits at Address 1D'h for Clause 22 format and/or C001'h for Clause 45 format, Table 3-28 and/or Table 3-33 respectively. The LOS indication is also available directly in the MDIO status registers, Address 01'h in Clause 22 format, see Table 3-9, and/or Address C009'h in Clause 45 format, see Table 3-31. The combination of all four drives the SIG DET pin (see Table 4-6), and contributes to the RX\_FAULT bit in the IEEE Status Register 2 at address (00)08'h (Table 3-14) and the LOCAL FLT bit in Register 0001'h, 1 in Table 3-10 (Clause 45 only).

As mentioned previously, LOS is designed as an indicator. The listed LOS threshold is for reference only, it is not designed to measure signal amplitude. Under nominal operation conditions, the actual LOS threshold is at a signal swing (single-ended peak-peak) lower or around the datasheet specified threshold. For a low LOS threshold setting, LOS may never be asserted due to noise.

## 3.7.3 Clock and Data Recovery

The line rate receive clock is extracted from the transition-rich 10-bit coded serial data stream independently on each channel. The data rate of the received serial bit stream for XAUI should be 3.125Gbps ±100ppm to guarantee proper reception (and similarily for other data rates). The receive clock locks to the input within 2µs after a valid input data stream is applied. The received data is de-serialized and byte-aligned.

The CDR unit will inherently acquire synchronization, provided the signal level is adequate, and the frequency is within the specified range of the local reference clock. If synchronization is lost due to an invalid signal (e.g. disconnect, out of range voltage swing, out of range frequency, etc.), then the high-speed receive clock will free run frequency-locked to the transmit clock.

# 3.7.4 Byte Alignment (code-group alignment)

Unless the CDET bits of the MDIO Register at address 10'h (Table 3-15, Clause 22) and/or C000'h (Table 3-32, Clause 45) are turned off, the Byte Alignment Unit is activated. The Byte Alignment Unit searches the coded incoming serial stream for a sequence defined in IEEE 802.3-2002 subclause 36.2.4.8 as a "comma". A comma is the sequence "0011111" or "1100000" and is uniquely located in a valid 8b/10b coded data stream, appearing as the start of some control symbols, including the /K/ IDLE. Any proprietary encoding scheme used should either incorporate these codes, or arrange byte alignment differently.

Comma disparity action can be controlled via the CDET bits. Upon detection of a comma, the Byte Alignment Unit shifts the incoming data to align the received data properly in the 10-bit character field. Two possible algorithms may be used for byte alignment. The default is to byte-align on any comma pattern. Although quick to align, and normally very reliable, this method is susceptible to realignment on certain single-bit errors or on successive K28.7 characters. The alternative algorithm is that specified in the IEEE802.3ae-2002 clause 48 specification, and is much less susceptible to error. Algorithm selection is controlled via MDIO register bit PCS\_SYNC\_EN at address 1D'h (Clause 22, Table 3-28) and/or C000'h (Clause 45, Table 3-32), unless overridden by the XAUI\_EN bit in the same registers. The recovered receive clocks may be stretched (never slivered) during byte alignment, but up to a full code group may be deleted or modified while aligning the "comma" code group correctly to the edges of the RefClock.

## 3.7.5 Data Decoding

The serial bit stream must be ordered "abcdeifghj" with "a" being the first bit received and "j" the last. With the 10b/8b XGMII decoder enabled, the decoded data is ordered "ABCDEFGHK" with "A" being the LSB. The decoding of valid 10b patterns is shown in Table 3-3 below. If the TRANS EN bit or XAUI\_EN bit (the MDIO Registers at Clause 22 addresses 10'h and 1D'h, see Table 3-15 and Table 3-28), and/or Clause 45 address C001'h, see Table 3-33) are set, all incoming XAUI IDLE patterns will be converted to the XGMII IDLE pattern set by the control register at address 1B'h (Clause 22 format) and/or C003'h (Clause 45 format), with a default value 107'h, the standard XGMII IDLE code (see Table 3-26). If neither bit is set, the incoming IDLE codes will all be decoded to the appropriate XGMII control code values. The first full column of IDLEs after any column containing a non-IDLE will be stored in the elasticity FIFO, and all subsequent full IDLE columns will repeat this pattern, until another column containing a non-IDLE is received.

If the BBT3420 XAUI\_EN bit is set or the PCS\_SYNC\_EN and DSKW\_SM\_EN bits are set, and the device has detected a 'Local Fault' (see Table 3-10, Table 3-14, Table 3-28 and/or Table 3-32 & Table 3-33), the XGMII output will consist of the Sequence control character in channel A (XAUI lane 0) and data characters of 0x00 in channels B & C (lanes 1 and 2) plus a data character of 0x01 in channel D (lane 3), the IEEE-defined ||LF|| Sequence Ordered\_Set.

TABLE 3-3. VALID 10b/8b DECODER PATTERNS

|                                                          | i | RECEIVING |         |                         |                                           |

|----------------------------------------------------------|---|-----------|---------|-------------------------|-------------------------------------------|

| SERIAL CODE, TRANS_EN CHARACTER BIT (Note 2) E-BIT K-BIT |   | K-BIT     | RD DATA | NOTES<br>DESCRIPTION    |                                           |

| Valid Data                                               | Х | 0         | 0       | 0-FF'h                  | Same Data Value as Transmitted            |

| /K/ (Sync) K28.5                                         | 1 | 0         | 1       | = XGMII IDLE (Note 3)   | Default 107'h                             |

|                                                          | 0 | 0         | 1       | BC                      | Comma (Note 1)                            |

| /A/ (Align) K28.3                                        | 1 | 0         | 1       | = XGMII IDLE (Note 3)   | Default 107'h                             |

|                                                          | 0 | 0         | 1       | 7C                      | Align (Note 1)                            |

| /R/ (Skip) K28.0                                         | 1 | 0         | 1       | = XGMII IDLE (Note 3)   | Default 107'h                             |

|                                                          | 0 | 0         | 1       | 1C                      | Alternate Idle (Note 1)                   |

| /S/ K27.7                                                | Х | 0         | 1       | FB                      | Start                                     |

| /T/ K29.7                                                | Х | 0         | 1       | FD                      | Terminate                                 |

| K28.1                                                    | Х | 0         | 1       | 3C                      | Extra comma                               |

| /F/ K28.2                                                | Х | 0         | 1       | 5C                      | Signal Ordered_Set marker                 |

| /Q/ K28.4                                                | Х | 0         | 1       | 9C                      | Sequence Ordered_Set marker               |

| K28.6                                                    | Х | 0         | 1       | DC                      |                                           |

| K28.7                                                    | Х | 0         | 1       | FC                      | Two will have caused byte realignment     |

| K23.7                                                    | Х | 0         | 1       | F7                      |                                           |

| /E/ K30.7                                                | Х | 1         | 1       | FE                      | Error                                     |

| Any other                                                | Х | 1         | = XC    | GMII ERROR reg.(Note 3) | Error Code, Default 1FF'h, see Table 3-19 |

## NOTES:

- 1. First incoming IDLE only, subsequent IDLEs in that block repeat first received code.

- 2. If the XAUI\_EN bit is set, the BBT3420 acts as though the TRANS\_EN bit is set.

- 3. The XGMII IDLE character is set by the XGMII IDLE register, address 1B'h/C003'h (see Table 3-26), default value 07'h, combined with the K bit. The XGMII ERROR code is similarly set by the XGMII ERROR register, address 16'h/C002'h (see Table 3-19)

#### 3.8 Receive FIFO

The Receive FIFO performs two functions:

- 1. Channel Alignment

- 2. Clock Compensation

## 3.8.1 CHANNEL ALIGNMENT (DESKEW)

Trunking, also known as deskewing, means the alignment of packet data across multiple channels. 8 byte of RXFIFO is dedicated for channel alignment.

During high-speed transmission, different active and passive elements in the links may impart varying delays in the four channels. In trunking mode, multiple channels share the same clock (local reference or recovered clock A), which is used for outputting data on the parallel bus.

As defined by IEEE 802.3ae-2002, packets must start on channel A (equivalent to Lane 0 in the IEEE 802.3ae-2002 specification). Deskewing is accomplished by monitoring the contents of the FIFOs to detect the boundary between IDLE sequences and any non-IDLE data (including data and the /S/

code), which defines the beginning of the packet, or the presence of the IEEE 802.3ae-defined /A/ character, for channel alignment (controlled by MDIO Register 19'h in Clause 22 format and/or C000'h in Clause 45 format, see Table 3-24 and/or Table 3-32). When this alignment data is detected in all four channels, the trunking channel-alignment operation is performed, and will be held until another such transition or /A/ character is detected again on any channel. To maintain channel alignment, such transitions or /A/ characters should occur on all four channels simultaneously (i.e. within the span of the FIFO). During channel realignment, up to four code groups may be deleted, repeated or garbled on any channel.

The deskew state machine is enabled by setting the DSKW\_SM\_EN bit (Clause 22 Address 1D'h see Table 3-28; Clause 45 Address C000'h see Table 3-32) to 1. The deskew algorithm is implemented according to IEEE spec. 802.3ae. Note that when DSKW\_SM\_EN is set to 1, the CAL\_EN bit (Clause 22 Address 19'h see Table 3-24; Clause 45 Address C000'h see Table 3-32) is ignored. When the DSKW\_SM\_EN bit is set to 0, channel deskew can still be enabled by setting

CAL\_EN, but the deskew action will be carried out without hysteresis.

The user has the option to disable trunking, or enable trunking across 4 channels, under control of the PSYNC pin (Table 4-6) and the RCLKMODE bits in the MDIO Registers at address 18'h in Clause 22 format and/or C000'h in Clause 45 format (see Table 3-21 and/or Table 3-32). In trunking mode, the channels may have phase differences, but they are expected to be frequency synchronous. In non-trunking mode, each received serial stream need only be within ±100ppm of 3.125Gbps (or 1.56125) Gbps. Note that trunking mode is only possible if 8b/10b Coding is activated, and all channels have the same half-rate setting (Table 3-30).

#### 3.8.2 CLOCK COMPENSATION

In addition to deskew, the Receive FIFO also compensates for clock differences. Since the received serial stream can, under worst-case conditions, be off by up to ±200ppm from the local clock domain (both can be up to ±100ppm from nominal), the received data must be adjusted to the local frequency. The received data can be aligned in one of three ways, under control of the PSYNC pin (Table 4-6) and the RCLKMODE bits in MDIO Register 18'h in Clause 22 format and/or C000'h in Clause 45 format (see Table 3-21 and/or Table 3-32):

- 1. Local Reference Clock (trunking mode)

- 2. Recovered Clock for each channel (non-trunking mode)

- 3. Recovered Clock for Channel A (trunking mode)

Another 8 bytes of RXFIFO are dedicated for clock compensation. The FIFOs achieve clock tolerance by identifying any of the IDLE patterns in the XAUI input (/K/, /A/ or /R/ as defined by the IEEE 802.3ae-2002 standard) in the received data and then adding or dropping IDLEs as needed. The Receive FIFO does not store the actual IDLE sequences received but generates the number of IDLEs needed to compensate for clock tolerance differences. See also Table 3-3 on page 8.

#### 3.9 Error Recovery

Errors in the high-speed links can be separated into two types, Loss of Signal and Coding Error violations. These are handled differently by the Error Recovery system in the BBT3420.

## 3.10 Disparity Error & Coding Violation

#### **3.10.1 XGMII 8 BIT MODE**

If 8b/10b encoding/decoding is turned on, the BBT3420 expects to receive a properly encoded serial bit stream. If the received data contains an error, the transceiver will report it as described below:

The received bits 0-7 represent the 8b/10b decoded value, bit 8 represents the K value and bit 9 indicates a disparity error or code error. In the event of a disparity error, the decoded value is passed to the parallel output [8..0], and bit 9 is asserted to indicate the error. If it is a coding error, the decoded value presented is a programmable error byte (default=K30.7).

Therefore the value for bit 0-8 is 1,1111,1110'b. Bit 9 is asserted to indicate the error.

This transceiver does not support the even/odd character mode specific to 1000Base-X operations. Byte alignment with comma is achieved with a 10-bit period. As a result, a comma received at any odd or even byte location, but at the proper byte boundary, will not cause any byte realignment.

#### 3.10.2 10-BIT MODE

If the 8b/10b Codec is inactive, disparity error and coding violation errors do not apply. System designers must ensure that the data stream is DC-balanced and contains sufficient transition density for proper operation, including synchronization. The required density depends on the frequency difference between the received data and the local reference clock, and the incoming signal jitter tolerance requirement. For a frequency difference of ±100ppm, and a transition-free data pattern of 500 successive 1's or 0's, the total build-up of CDR timing error is 0.1 UI. If this pattern is followed by a pattern of normal density, the reduction of jitter tolerance will usually be acceptable, though if such long notransition patterns are common, the jitter buildup could be cumulative. In a fully synchronous system, where there are no consistent frequency differences, these effects are of course reduced.

#### 3.10.3 OUTPUT SELECT - PARALLEL LOOPBACK

In normal mode, the serial input data RX[A..D]P/N data will be placed on the parallel receive outputs RD[A..D][9..0]. When parallel loopback is activated, the internal parallel output is routed to the parallel input (including clock) for every channel. The RD[A..D][9..0] pins may be disabled if desired, whether in parallel output mode or not, by using the IPON bit of the MDIO Register at address 011'h (Clause 22 see Table 3-16) and/or address C001'h (Clause 45, see Table 3-33).

| TARIF 3-4 MDI | O MANAGEMENT | FRAME FORMATS |

|---------------|--------------|---------------|

|                                                           | Clause 22 Format (from Table 22-10 in IEEE Std 802.3-2002) |    |    |       |       |    |                 |      |  |  |

|-----------------------------------------------------------|------------------------------------------------------------|----|----|-------|-------|----|-----------------|------|--|--|

| Opern                                                     | PRE                                                        | ST | OP | PHYAD | REGAD | TA | DATA            | IDLE |  |  |

| Read                                                      | 11                                                         | 01 | 10 | PPPPP | RRRRR | Z0 | DDDDDDDDDDDDDD  | Z    |  |  |

| Write                                                     | 11                                                         | 01 | 01 | PPPPP | RRRRR | 10 | DDDDDDDDDDDDDDD | Z    |  |  |

| Clause 45 Format (from Table 45-64 in IEEE 802.3.ae-2002) |                                                            |    |    |       |       |    |                 |      |  |  |

| Opern                                                     | PRE                                                        | ST | OP | PRTAD | DEVAD | TA | ADDRESS/DATA    | IDLE |  |  |

| Addrs                                                     | 11                                                         | 00 | 00 | PPPPP | DDDDD | 10 | AAAAAAAAAAAAA   | Z    |  |  |

| Write                                                     | 11                                                         | 00 | 01 | PPPPP | DDDDD | 10 | DDDDDDDDDDDDDD  | Z    |  |  |

| Read                                                      | 11                                                         | 00 | 11 | PPPPP | DDDDD | Z0 | DDDDDDDDDDDDDD  | Z    |  |  |

| Read Inc                                                  | 11                                                         | 00 | 10 | PPPPP | DDDDD | Z0 | DDDDDDDDDDDDDD  | Z    |  |  |

## 3.11 Serial Management Interface

The BBT3420 implements both the Management Interface defined in IEEE 802.3 Clause 22, and that defined in Clause 45. This two-pin interface allows serial read/write of the internal control registers and consists of the MDC clock and MDIO data terminals. The PADR[4..0] pins are used to select the address to which a given BBT3420 device responds. The remainder of the MDIO frame and access details depend on the respective formats. The BBT3420 automatically detects which format is being used on a frame-by-frame basis, based on the second START bit. The two formats are shown in Table 3-4, together with the references to the respective IEEE 802.3 specifications. The fields are as follows:

- PRE, the Preamble field: at least 32 consecutive '1' bits. The BBT3420 will accept any number ≥32.

- ST, the Start of Frame; for Clause 22, <01>; for Clause 45, <00>.

- OP, the Operation code; for Clause 22, Read and Write operations are defined, all other values are invalid; for Clause 45, additional operations to send the 16-bit (indirect) register address, and to read data and (then) increment the stored address are added.

- PHYAD/PRTAD; the PHYsical (Clause 22) or PoRT (Clause 45) hardware ADdress; this 5-bit address must match the PADR pins on the BBT3420.

- REGAD, REGister ADdress (Clause 22); this 5-bit address specifies the register address. Replaced by the 16-bit address value in Clause 45 format.

- DEVAD, DEVice ADdress (Clause 45); this 5-bit address specifies which MMD at any given port is being addressed.

See Table 3-5 and section 3.13 for the possible values the BBT3420 will respond to.

- TA, the TurnAround; allows time to avoid contention for a read operation on the MDIO line.

- DATA; the 16 bit data values to be written to or being read from the BBT3420.

- ADDRESS (Clause 45); this 16-bit address specifies the register address for subsequent Clause 45 read or write

operations. A Read Increment operation will post-increment the value.

• IDLE; this condition flags the end of the frame. Since the IEEE specification calls for a pullup on the MDIO line, this effectively provides the MMD with a '1' character, which can be the beginning of the next PREamble.

TABLE 3-5. DEVAD DEVICE ADDRESS SETUP TABLE

| MFD | MFC | DEVAD<br>VALUE          | DEFAULT | IEEE<br>DEFINITION      |

|-----|-----|-------------------------|---------|-------------------------|

| 1   | 1   | DEVAD = 5<br>(000101'b) | 11'b    | DTE XS (XGXS<br>Device) |

| 1   | 0   | DEVAD = 4<br>(00100'b)  |         | PHY XS (XGXS<br>Device) |

| 0   | 1   | DEVAD = 31<br>(11111'b) |         | Vendor Specific         |

| 0   | 0   | DEVAD = 30<br>(11110'b) |         | Vendor Specific         |

## 3.12 Clause 22 PHY Addressing

The PADR[4..0] hardware address pins control the PHYAD value, allowing use of up to 31 BBT3420 (or other compatible) devices on any MDC/MDIO line pair. Each device may contain up to 32 registers, some of which are defined by the IEEE standard, the others being Vendor-defined. The Clause 22-accessible registers are listed in Table 3-6.

## 3.13 Clause 45 PHY Addressing

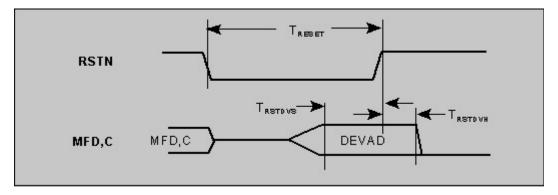

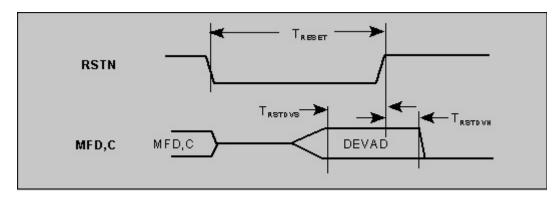

The PADR[4..0] hardware address pins control the PRTAD (Port Address) value, each port normally consisting of a series of MDIO Managed Devices (MMDs). Each of the up to 31 Ports may include up to 31 different devices, of which the current specification defines 6 types, and allows vendor specification of two others. The native-mode BBT3420 corresponds to two of the defined types; it can be either a PHY XS (DEVAD = 4) or a DTE XS (DEVAD = 5), but may also be used as part of another defined type, or as a RETIMER function. The device may be set to respond to any one of four DEVAD values, (4, 5, 30 or 31) by controlling the level on the MFC and MFD pins at the end of reset. These pins are normally outputs, but become

inputs when RSTN is active, and so may be pulled to the desired value by moderate value resistors ( $\sim\!5 \text{k}\Omega$ ), which will not affect the normal operation of the pins when outputs. The value on these pins will be latched at the rising edge of RSTN. The coding is shown in Table 3-5. A weak pullup is built into these pins, so that if unwired, they will default to DEVAD = 5. See Table 6-13 and Figure 6-9 for the timing of these signals. The Clause 45-accessible registers are listed in Table 3-7. These register addresses are independent of the DEVAD value, including the 'Vendor Defined' DEVAD values 30 & 31; thus registers 30.8 & 31.8 include the RX\_FAULT and TX\_FAULT bits.

Each individual device may have up to 2<sup>16</sup> (65,536) registers. The BBT3420 implements 11 of the IEEE-defined registers for PHY XS and DTE XS devices (they may be accessed identically through any of the implemented DEVAD address

values), and 11 of the 32k (2<sup>15</sup>) allowed Vendor Specific registers. The latter have been placed in the block beginning at C000'h so as to avoid the areas currently defined as for use by the XENPAK module and similar MSA devices, to facilitate use of the BBT3420 in systems using such modules and/or devices.

In order to align the registers and bits as closely as possible to the new IEEE Clause 45 standard, while maintaining compatibility with previous versions of the part before the Clause 45 interface was defined, which used only the Clause 22 interface, the control and status bits are differently distributed among the registers in the two formats. The Clause 22 registers are listed in Table 3-6, and the Clause 45 registers in Table 3-7.

TABLE 3-6. MDIO REGISTERS IN CLAUSE 22 FORMAT

|         | MII REGISTERS            |                                            |                 |       |              |  |  |  |  |  |

|---------|--------------------------|--------------------------------------------|-----------------|-------|--------------|--|--|--|--|--|

| ADDRESS | NAME                     | DESCRIPTION                                | DEFAULT         | R/W   | DETAILS      |  |  |  |  |  |

| 00'h    | Control                  | Reset, Enable serial loop back mode.       | 2040'h          | R/W   | Table 3-8    |  |  |  |  |  |

| 01'h    | Status                   | Device Present & LOS                       | 800F'h (Note 2) | RO    | Table 3-9    |  |  |  |  |  |

| 02:3'h  | ID Code                  | Manufacturer and Device OUI & IDs          | 01839C5V'h      | RO    | See (Note 1) |  |  |  |  |  |

| 04'h    | Speed Ability            | 10Gbps Ability                             | 0001'h          | RO    | Table 3-11   |  |  |  |  |  |

| 05'h    | IEEE Devices             | Devices in Package, Clause 22 capable      | 0021'h (Note 3) | RO    | Table 3-12   |  |  |  |  |  |

| 06'h    | Vendor Devices           | Vendor Specific Devices in Package         | 0000'h (Note 3) | RO    | Table 3-13   |  |  |  |  |  |

| 08'h    | Fault Status             | Transmit & Receive Fault                   | 8000'h (Note 2) | RO/LH | Table 3-14   |  |  |  |  |  |

| 10'h    | Misc. Control 1          | Channel, Comma, TX Idle, MF controls       | 00C0'h          | R/W   | Table 3-15   |  |  |  |  |  |

| 11'h    | Misc. Control 2          | Code, Comma, Codec, TCx controls           | 0140'h          | R/W   | Table 3-16   |  |  |  |  |  |

| 12'h    | Special Control Register | DC Offset & RC[A:D] phase shift control    | 0000'h          | R/W   | Table 3-17   |  |  |  |  |  |

| 13'h    | Resvd2                   | Spare Status                               | 0000'h          | RO    | Table 3-18   |  |  |  |  |  |

| 16'h    | ERROR                    | Sets XGMII ERROR Code                      | 0FF'h           | R/W   | Table 3-19   |  |  |  |  |  |

| 17'h    | Loop Back                | Controls Serial & Parallel Loopback        | 0000'h          | R/W   | Table 3-20   |  |  |  |  |  |

| 18'h    | Receive Clock            | Receive Clock Mode                         | 0001'h          | R/W   | Table 3-21   |  |  |  |  |  |

| 19'h    | Symbol                   | IDLE, Alignment and Elasticity Control     | 000F'h          | R/W   | Table 3-24   |  |  |  |  |  |

| 1A'h    | Errors                   | Error Flags                                | 0000'h (Note 2) | RO    | Table 3-25   |  |  |  |  |  |

| 1B'h    | XGMII IDLE               | XGMII-side IDLE Code                       | 0007'h          | R/W   | Table 3-26   |  |  |  |  |  |

| 1C'h    | Boost/Pre-emp            | Boost and Pre-emphasis Control             | 0000'h          | R/W   | Table 3-27   |  |  |  |  |  |

| 1D'h    | Misc. Control 3          | V <sub>DDQ</sub> , LOS, RC timing, /A/K/R/ | 0000'h          | R/W   | Table 3-28   |  |  |  |  |  |

| 1E'h    | Internal Test            |                                            | AAAA'h          | R/W   | Table 3-29   |  |  |  |  |  |

| 1F'h    | Half Rate                | Half-rate clock mode enable                | 0000'h          | R/W   | Table 3-30   |  |  |  |  |  |

#### NOTES:

- 1. 'V' is a version number. See under "3.15 JTAG" on page 22 for a note about the version number.

- 2. Read value depends on status signal values. Value shown indicates 'normal' operation.

- 3. Read value depends on DEVAD setting, see Table 3-5 and Figure 6-9 for details.

TABLE 3-7. MDIO REGISTERS IN CLAUSE 45 FORMAT

| MII REGISTERS |                          |                                              |                 |        |              |  |  |  |  |

|---------------|--------------------------|----------------------------------------------|-----------------|--------|--------------|--|--|--|--|

| ADDRESS       | NAME                     | DESCRIPTION                                  | DEFAULT         | R/W    | DETAILS      |  |  |  |  |

| 0000'h        | XGXS Control 1           | Reset, Enable serial loop back mode.         | 2040'h          | R/W    | Table 3-8    |  |  |  |  |

| 0001'h        | XGXS Status 1            | Fault, Link Status                           | 0004'h (Note 2) | RO LL  | Table 3-10   |  |  |  |  |

| 0002:3'h      | ID Code                  | Manufacturer and Device OUI & IDs            | 01839C5V'h      | RO     | See (Note 1) |  |  |  |  |

| 0004'h        | Speed Ability            | 10Gbps Ability                               | 0001'h          | RO     | Table 3-11   |  |  |  |  |

| 0005'h        | IEEE Devices             | Devices in Package, Clause 22 capable        | 0021'h(3)       | RO     | Table 3-12   |  |  |  |  |

| 0006'h        | Vendor Devices           | Vendor Specific Devices in Package           | 0000'h(3)       | RO     | Table 3-13   |  |  |  |  |

| 0008'h        | XGXS Status 2            | Device Present, Local Fault                  | 8000'h (Note 2) | RO     | Table 3-14   |  |  |  |  |

| 0018'h        | 10G Lane Status          | Receive Channels Aligned, Synched            | 100F'h (Note 2) | RO     | Table 3-23   |  |  |  |  |

| C000'h        | Misc. Control 1          | V <sub>DDQ</sub> , RC, Code, Comma, Stt Mach | lach 072F'h R/W |        | Table 3-32   |  |  |  |  |

| C001'h        | Misc. Control 2          | BIST, LOS, XAUI, TX, MF controls             | 0010'h R/W      |        | Table 3-33   |  |  |  |  |

| C002'h        | ERROR                    | Sets XGMII ERROR Code                        | 0FF'h           | R/W    | Table 3-19   |  |  |  |  |

| C003'h        | XGMII IDLE               | XGMII-side IDLE Code                         | 0007'h          | R/W    | Table 3-26   |  |  |  |  |

| C004'h        | Loop Back                | Controls Serial & Parallel Loopback          | 0000'h          | R/W    | Table 3-20   |  |  |  |  |

| C005'h        | Boost/Pre-emp            | Boost and Pre-emphasis Control               | 0000'h          | R/W    | Table 3-27   |  |  |  |  |

| C006'h        | Errors                   | Error Flags                                  | 0000'h (Note 2) | RO     | Table 3-25   |  |  |  |  |

| C007'h        | Special Function         | MUST be left at Default Value                | AAAA'h          | R/W    | Table 3-29   |  |  |  |  |

| C008'h        | Half Rate                | Half-rate clock mode enable                  | 0000'h          | R/W    | Table 3-30   |  |  |  |  |

| C009'h        | LOS Status               | LOS Channel Status                           | 00F0'h (Note 2) | RO LH  | Table 3-31   |  |  |  |  |

| C00A'h        | Special Control Register | DC Offset & RC[A:D] phase shift control      | 0000'h          | R/W    | Table 3-17   |  |  |  |  |

| C00B'h        | Reserved                 | Spare Status                                 | 0000'h          | RO     | Table 3-18   |  |  |  |  |

| C00F'h        | Soft Reset               | Reset (non-MDIO)                             | 0000'h          | R/W SC | Table 3-34   |  |  |  |  |

## NOTES:

- 4. 'V' is a version number. See JTAG on page 25 for a note about the version number.

- 5. Read value depends on status signal values. Value shown indicates 'normal' operation.

- 6. Read value depends on DEVAD setting, see Table 3-5 and Figure 6-9 for details.

## 3.14 MDIO Registers

In the following tables, the Clause 45 addresses are given after the Clause 22 address in the table header, where the registers coincide in structure, but the addresses differ. Separate tables are given for registers and bits differently constructed. The underlying register bits are the same, and may be read or written indiscriminately in either format (except for a few bits that are not accessible via the Clause 22 format).

TABLE 3-8. IEEE XGXS CONTROL 1 REGISTER

| MII REGISTER 0, ADDRESSES = 00'h & 0000'h |           |                |         |        |                                                           |  |  |  |

|-------------------------------------------|-----------|----------------|---------|--------|-----------------------------------------------------------|--|--|--|

| BIT                                       | NAME      | SETTING        | DEFAULT | R/W    | DESCRIPTION                                               |  |  |  |

| 15                                        | Reset     | 1 = reset      | 0'b     | R/W SC | Self-clearing reset. Writing 1 to this bit will reset the |  |  |  |

|                                           |           | 0 = reset done |         |        | whole chip, including the MDIO registers.                 |  |  |  |

| 14                                        | LOOP_EN   | 1 = enable     | 0'b     | R/W    | Enable serial loopback mode.                              |  |  |  |

| 13                                        | SPEEDSEL0 | 1 = 10Gbps     | 1'b     | RO     | Writes ignored                                            |  |  |  |

| 12                                        | Reserved  |                |         |        |                                                           |  |  |  |

| 11                                        | LOPOWER   | 1 = Low Power  | 0'b     | R/W    | No Low Power Mode, ignored                                |  |  |  |

| 10:7                                      | Reserved  |                |         |        |                                                           |  |  |  |

| 6                                         | SPEEDSEL1 | 1 = 10Gbps     | 1'b     | RO     | Writes ignored                                            |  |  |  |

| 5:2                                       | SPEEDSEL  | 0 = 10Gbps     | 0'h     | RO     | Writes ignored                                            |  |  |  |

| 1:0                                       | Reserved  |                |         |        |                                                           |  |  |  |

TABLE 3-9. IEEE XGXS STATUS 1 REGISTER (CLAUSE 22)

| MII REGISTER 1, ADDRESS = 01'h |                |                              |         |       |                                                                         |  |  |  |

|--------------------------------|----------------|------------------------------|---------|-------|-------------------------------------------------------------------------|--|--|--|

| BIT                            | NAME           | SETTING                      | DEFAULT | R/W   | DESCRIPTION                                                             |  |  |  |

| 15:14                          | Device present | 10 = Device present          | 10'b    | RO    | Indicates that a device is present at this device address               |  |  |  |

| 13                             | LOS_D          | 1 = Signal less              | 0'b     | RO/LH | Loss Of Signal for RX Inputs of each of 4 channels; signal              |  |  |  |

| 12                             | LOS_C          | than threshold<br>0 = Signal | 0'b     |       | less than LOS_CONTROL value (see Table 3-28 and/or Table 3-33) (Note 1) |  |  |  |

| 11                             | LOS_B          | greater than<br>threshold    | 0'b     |       | , ,                                                                     |  |  |  |

| 10                             | LOS_A          | triresnoid                   | 0'b     |       |                                                                         |  |  |  |

| 9:4                            | Reserved       |                              | 00'h    | RO    |                                                                         |  |  |  |

| 3:0                            | Internal       |                              | F'h     | RO    | Internal Function (ignore)                                              |  |  |  |

#### NOTE:

1. Please refer to section "3.7.2 Loss of Signal (LOS)" on page 6 for a more detailed description.

## TABLE 3-10. IEEE XGXS STATUS 1 REGISTER (CLAUSE 45)

|      | MII REGISTER 1, ADDRESS = 0001'h |                   |         |       |                              |  |  |  |  |

|------|----------------------------------|-------------------|---------|-------|------------------------------|--|--|--|--|

| BIT  | NAME                             | SETTING           | DEFAULT | R/W   | DESCRIPTION                  |  |  |  |  |

| 15:8 | Reserved                         |                   | 00'h    | RO    |                              |  |  |  |  |

| 7    | LOCAL_FLT                        | 1 = Local Fault   | 0'b     | RO    | Derived from Register 0008'h |  |  |  |  |

| 6:3  | Reserved                         |                   |         |       |                              |  |  |  |  |

| 2    | RX_LINK                          | 1 = XGXS Link up  | 1'b     | RO LL | XAUI Receive Link Status     |  |  |  |  |

| 1    | LoPwrAble                        | Low Power Ability | 0'b     | RO    | Does not support Low Power   |  |  |  |  |

| 0    | Reserved                         |                   |         |       |                              |  |  |  |  |

## **TABLE 3-11. IEEE SPEED ABILITY REGISTER**

| MII REGISTER 4, ADDRESSES = 04'h & 0004'h |          |                 |         |     |              |  |  |  |

|-------------------------------------------|----------|-----------------|---------|-----|--------------|--|--|--|

| BIT                                       | NAME     | SETTING         | DEFAULT | R/W | DESCRIPTION  |  |  |  |

| 15:1                                      | Reserved |                 | 000'h   | RO  |              |  |  |  |

| 0                                         | 10G_Able | 1 = 10Gbps Able | 1'b     | RO  | 10GE Capable |  |  |  |

## TABLE 3-12. IEEE DEVICES IN PACKAGE REGISTER

|      | MII REGISTER 5, ADDRESSES = 05'h & 0005'h |                    |            |     |                                         |  |  |  |  |  |

|------|-------------------------------------------|--------------------|------------|-----|-----------------------------------------|--|--|--|--|--|

| BIT  | NAME                                      | SETTING            | DEFAULT    | R/W | DESCRIPTION                             |  |  |  |  |  |

| 15:7 | Reserved                                  |                    | 000'h      | RO  |                                         |  |  |  |  |  |

| 6    | TC                                        | TC present         | 0'b        | RO  | Device ignores DEVAD 6 (TC not present) |  |  |  |  |  |

| 5    | DTE XS                                    | 1 = DTE XGXS       | P (Note 1) | RO  | Device responds to DEVAD 5              |  |  |  |  |  |

| 4    | PHY XS                                    | 1 = PHY XGXS       | P (Note 1) | RO  | Device responds to DEVAD 4              |  |  |  |  |  |

| 3    | PCS                                       | 1 = PCS            | 0'b        | RO  | Device ignores DEVAD 3                  |  |  |  |  |  |

| 2    | WIS                                       | 1 = WIS            | 0'b        | RO  | Device ignores DEVAD 2                  |  |  |  |  |  |

| 1    | PMD/PMA                                   | 1 = PMD/PMA        | 0'b        | RO  | Device ignores DEVAD 1                  |  |  |  |  |  |

| 0    | Cls 22 Regs                               | 1 = MDIO Clause 22 | 1'b        | RO  | Device responds to Clause 22            |  |  |  |  |  |

## NOTE:

1. Value depends on DEVAD setting; see Table 3-5. 1 = responds, 0 = does not respond.

## TABLE 3-13. VENDOR SPECIFIC DEVICES IN PACKAGE REGISTER

|      | MII REGISTER 6, ADDRESSES = 06'h & 0006'h |                   |            |     |                                            |  |  |  |  |  |

|------|-------------------------------------------|-------------------|------------|-----|--------------------------------------------|--|--|--|--|--|

| BIT  | NAME                                      | SETTING           | DEFAULT    | R/W | DESCRIPTION                                |  |  |  |  |  |

| 15   | Vend Spec                                 | 1 = V S D present | S (Note 1) | RO  | Vendor Specific Device Present in Package  |  |  |  |  |  |

| 14   | Reserved                                  |                   | 0'b        | RO  |                                            |  |  |  |  |  |

| 13   | Ext. Cls 22                               |                   | 0'b        | RO  | No extended Clause 22 registers in Package |  |  |  |  |  |

| 12:0 | Reserved                                  |                   | 000'h      | RO  |                                            |  |  |  |  |  |

## NOTE:

1. Value depends on DEVAD setting; see Table 3-5. 1 = responds, 0 = does not respond.

## **TABLE 3-14. IEEE XGXS STATUS2 REGISTER**

|       | MII REGISTER 8, ADDRESSES = 08'h & 0008'h |                     |         |                   |                                                                                                                            |  |  |  |  |

|-------|-------------------------------------------|---------------------|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT   | NAME                                      | SETTING             | DEFAULT | R/W               | DESCRIPTION                                                                                                                |  |  |  |  |

| 15:14 | Device present                            | 10 = Device present | 10'b    | RO                | Indicates a device is present at this device address                                                                       |  |  |  |  |

| 13:12 | Reserved                                  |                     |         |                   |                                                                                                                            |  |  |  |  |

| 11    | TX_FAULT                                  | 1 = Tx Local Fault  | 0'b     | RO LH<br>(Note 1) | Transmit Fault Detector. Always 0                                                                                          |  |  |  |  |

| 10    | RX_FAULT                                  | 1 = Rx Local Fault  | 0'b     | RO LH<br>(Note 1) | Derived from Reg. 0024'h, Byte Sync and Alignment bits (not accessible via Clause 22), and 01'h/C009'h Loss Of Signal bits |  |  |  |  |

| 9:0   | Reserved                                  |                     |         |                   |                                                                                                                            |  |  |  |  |

## NOTE:

2. These bits are latched high on any fault condition detected. They are reset low upon being read.

TABLE 3-15. MISCELLANEOUS CONTROL REGISTER 1 (CLAUSE 22)

|      |           | MII REGIS                                                                                                        | TER 16, AD | DRESS = | : 10'h                                                                                                                                                                                                                       |

|------|-----------|------------------------------------------------------------------------------------------------------------------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT  | NAME      | SETTING                                                                                                          | DEFAULT    | R/W     | DESCRIPTION                                                                                                                                                                                                                  |

| 15:8 | Reserved  |                                                                                                                  |            |         |                                                                                                                                                                                                                              |

| 7:6  | CDET[1:0] | Bit 7 controls positive comma detection,<br>Bit 6 controls negative comma detection<br>0'b=disable<br>1'b=enable | 11'b       | R/W     | Comma Detect Select. These bits enable detection of positive, negative, or both positive and negative disparities of comma, or disable detection of either.                                                                  |

| 5:4  | Reserved  |                                                                                                                  |            |         |                                                                                                                                                                                                                              |

| 3    | TRANS_EN  | 1=enable<br>0=disable                                                                                            | 0'b        | R/W     | Enables transceiver to translate an "IDLE" pattern in the XGMII data (matching the value of register 1B'h) to and from the XAUI IDLE /K/ comma character or /A/, /K/ & /R/ characters. Overridden by XAUI_EN; see Table 3-28 |

| 2:0  | MF_CTRL   | TRL 0 = BIST_ERR 1 = LOS 2 = Reserved 3 = RC[A:D] 4 = TXFIFO_ERR 5 = AFIFO_ERR 6 = EFIFO_ERR                     |            | R/W     | Control the functions of multi-function pins MF[A-D]. RC[A:D] is recovered clock for each channel [A:D].                                                                                                                     |

TABLE 3-16. MISCELLANEOUS CONTROL REGISTER 2 (CLAUSE 22)

|       | MII REGISTER 17, ADDRESS = 11'h |                                                           |         |     |                                                                                                 |  |  |  |  |  |

|-------|---------------------------------|-----------------------------------------------------------|---------|-----|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIT   | NAME                            | SETTING                                                   | DEFAULT | R/W | DESCRIPTION                                                                                     |  |  |  |  |  |

| 15    | SHRT_BIST                       | 1 = Short BIST Loop pattern<br>0 = Long BIST Loop pattern | 0'b     | R/W | Short is 13458 Byte pattern, Long is 2 <sup>23</sup> -1 Byte Pattern (plus 9 /K/ "Comma" bytes) |  |  |  |  |  |

| 14:13 | Reserved                        |                                                           |         |     |                                                                                                 |  |  |  |  |  |

| 12    | BIST_EN                         | 1 = enable BIST Pattern<br>0 = disable                    | 0'b     | R/W | Built In Self Test (BIST) may also be enabled by the BIST_EN pin or via the JTAG system.        |  |  |  |  |  |

| 11:9  | Reserved                        |                                                           |         |     |                                                                                                 |  |  |  |  |  |

| 8     | IPON                            | 1=enable<br>0=disable                                     | 1'b     | R/W | Internal Parallel Output Enable                                                                 |  |  |  |  |  |

| 7     | Reserved                        |                                                           |         |     |                                                                                                 |  |  |  |  |  |

| 6     | CODECENA                        | CODECENA 1=enable if CODE pin hi 0=disable                |         | R/W | Internal 8b/10b Codec enable/disable                                                            |  |  |  |  |  |

| 5     | SC_TBC                          | 1=source sync<br>0=source center                          | 0'b     | R/W | Timing of incoming Transmit Byte Clock (TBC) to transmit data                                   |  |  |  |  |  |

| 4:0   | Reserved                        |                                                           |         |     |                                                                                                 |  |  |  |  |  |

## TABLE 3-17. SPECIAL CONTROL REGISTER

|      | MII REGISTER 18 & 49162, ADDRESSES = 12'h & C00A'h |                                                                   |         |     |                                                                           |  |  |  |  |  |

|------|----------------------------------------------------|-------------------------------------------------------------------|---------|-----|---------------------------------------------------------------------------|--|--|--|--|--|

| BIT  | BIT NAME SETTING                                   |                                                                   | DEFAULT | R/W | DESCRIPTION                                                               |  |  |  |  |  |

| 15   | EQ_DC_D                                            | 1=DC offset correction disable.<br>0=DC offset correction enable. | 0'b     | R/W | Channel D receive differential input DC offset correction disable/enable. |  |  |  |  |  |

| 14   | EQ_DC_C                                            | 1=DC offset correction disable.<br>0=DC offset correction enable. | 0'b     | R/W | Channel C receive differential input DC offset correction disable/enable. |  |  |  |  |  |

| 13   | EQ_DC_B                                            | 1=DC offset correction disable.<br>0=DC offset correction enable. | 0'b     | R/W | Channel B receive differential input DC offset correction disable/enable. |  |  |  |  |  |

| 12   | EQ_DC_A                                            | 1=DC offset correction disable.<br>0=DC offset correction enable. | 0'b     | R/W | Channel A receive differential input DC offset correction disable/enable. |  |  |  |  |  |

| 11:8 | Reserved                                           |                                                                   |         |     |                                                                           |  |  |  |  |  |

| 7:4  | Reserved                                           |                                                                   | 0'b     |     |                                                                           |  |  |  |  |  |

| 3    | RCD_Invert                                         | 1=invert phase, 0=default phase                                   | 0'b     | R/W | Invert RCD clock phase (RCD shift by 180 degrees)                         |  |  |  |  |  |

| 2    | RCC_Invert                                         | 1=invert phase, 0=default phase                                   | 0'b     | R/W | Invert RCC clock phase (RCC shift by 180 degrees)                         |  |  |  |  |  |

| 1    | RCB_Invert                                         | 1=invert phase, 0=default phase                                   | 0'b     | R/W | Invert RCB clock phase (RCB shift by 180 degrees)                         |  |  |  |  |  |

| 0    | RCA_Invert                                         | 1=invert phase, 0=default phase                                   | 0'b     | R/W | Invert RCA clock phase (RCA shift by 180 degrees)                         |  |  |  |  |  |

## TABLE 3-18. SPARE STATUS REGISTER

|      | MII REGISTER 19 & 49163, ADDRESSES = 13'h & C00B'h |  |  |  |  |  |  |  |

|------|----------------------------------------------------|--|--|--|--|--|--|--|

| BIT  | NAME SETTING DEFAULT R/W DESCRIPTION               |  |  |  |  |  |  |  |

| 15:0 | Reserved                                           |  |  |  |  |  |  |  |

## TABLE 3-19. XGMII ERROR CODE REGISTER

|      | MII REGISTER 22 & 49154, ADDRESSES = 16'h & C002'h |         |         |     |                                                                                                                            |  |  |  |

|------|----------------------------------------------------|---------|---------|-----|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BIT  | NAME                                               | SETTING | DEFAULT | R/W | DESCRIPTION                                                                                                                |  |  |  |

| 15:9 | Reserved                                           |         |         |     |                                                                                                                            |  |  |  |

| 8:0  | ERROR                                              | N/A     | 1FF'h   | R/W | Error Code. These bits allow the ERROR character to be programmed. Overridden by XAUI_EN, see Table 3-28 and/or Table 3-33 |  |  |  |

## TABLE 3-20. LOOP BACK CONTROL REGISTER

|       | MII REGISTER 23 & 49156, ADDRESSES = 17'h & C004'h |           |         |     |                                                                                                                                                             |  |  |  |  |

|-------|----------------------------------------------------|-----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT   | NAME                                               | SETTING   | DEFAULT | R/W | DESCRIPTION                                                                                                                                                 |  |  |  |  |

| 15:12 | Reserved                                           |           |         |     |                                                                                                                                                             |  |  |  |  |

| 11    | SLP_D                                              | 1=enable  | 0'h     | R/W | Internal Serial Loop Back Enable. These bits enable the loopback function                                                                                   |  |  |  |  |

| 10    | SLP_C                                              | 0=disable |         |     | for serial data for each individual channel. When high, they route the internal output of the Serializer to the input of the clock recovery block.          |  |  |  |  |

| 9     | SLP_B                                              |           |         |     |                                                                                                                                                             |  |  |  |  |

| 8     | SLP_A                                              |           |         |     |                                                                                                                                                             |  |  |  |  |

| 7:4   | Reserved                                           |           |         |     |                                                                                                                                                             |  |  |  |  |

| 3     | PLP_D                                              | 1=enable  | 0'h     | R/W | Internal Parallel Loop Back Enable. These bits enable the loopback                                                                                          |  |  |  |  |

| 2     | PLP_C                                              | 0=disable |         |     | function for parallel data for each individual channel. When high, it routes the internal output of the Deserializer to the parallel input of each channel. |  |  |  |  |

| 1     | PLP_B                                              |           |         |     |                                                                                                                                                             |  |  |  |  |

| 0     | PLP_A                                              |           |         |     |                                                                                                                                                             |  |  |  |  |

## TABLE 3-21. RECEIVE CLOCK MODE REGISTER (CLAUSE 22)

|      | MII REGISTER 24, ADDRESS = 18'h (CLAUSE 22) |                                                                            |         |     |                                                                                                                                    |  |  |  |  |

|------|---------------------------------------------|----------------------------------------------------------------------------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BIT  | NAME                                        | SETTING                                                                    | DEFAULT | R/W | DESCRIPTION                                                                                                                        |  |  |  |  |

| 15:2 | Reserved                                    |                                                                            |         |     |                                                                                                                                    |  |  |  |  |

| 1:0  | RCLKMODE                                    | Depends on RETIMER and PSYNC pins (Table 4-6). See settings in Table 3-22. | 01'b    | R/W | Received Clock Mode. These two bits, together with the PSYNC and RETIMER pins, select which clock the received data is aligned to. |  |  |  |  |

## TABLE 3-22. RCLKMODE BIT SETTINGS = 18'h.1:0 (CLAUSE 22) or C000'h.6:5 (CLAUSE 45)

| PIN NAME, LOGIC LEVEL |       | REGISTER CHANNEL |           | RCLKMODE BITS, and PIN VALUES, to           |  |  |

|-----------------------|-------|------------------|-----------|---------------------------------------------|--|--|

| RETIMER               | PSYNC | BIT SETTING      | ALIGNMENT | RECEIVE DATA CLOCK ALIGNMENT                |  |  |

| 0                     | 0     | XX               | No        | Local Reference Clock                       |  |  |

| 0                     | 1     | XX               | Yes       | Local Reference Clock                       |  |  |

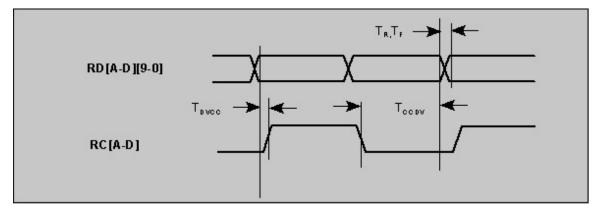

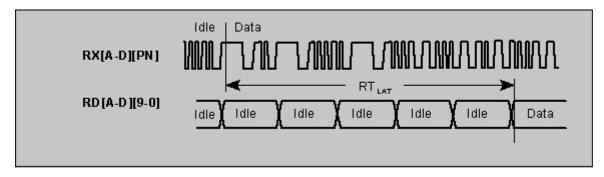

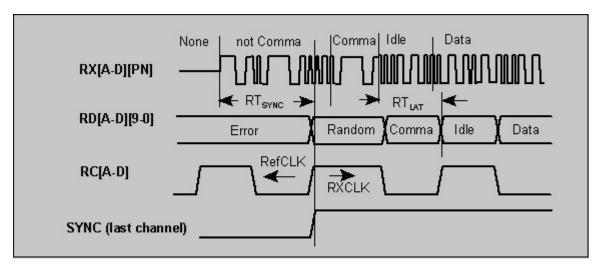

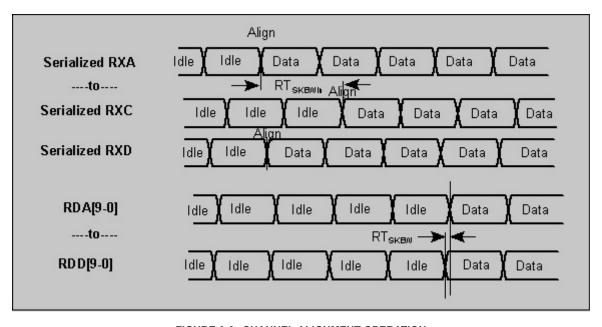

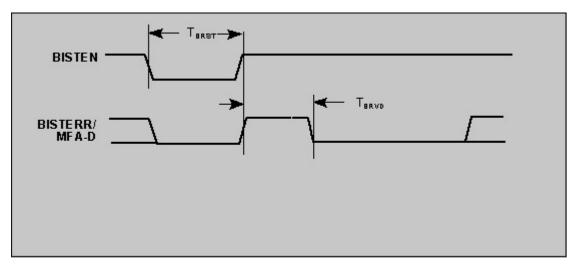

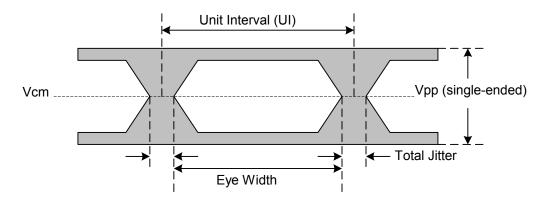

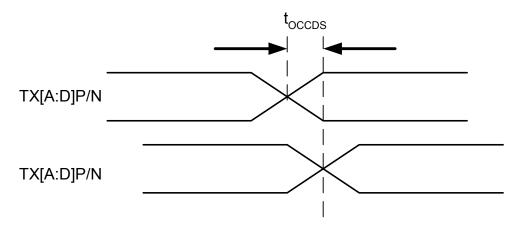

| Х                     | 0     | 11'b             | No        | Local Reference Clock                       |  |  |