# Low Phase Noise, Fast Settling PLL **Frequency Synthesizer**

## **Data Sheet**

# **ADF4193**

## **FEATURES**

New, fast settling, fractional-N PLL architecture Single PLL replaces ping-pong synthesizers Frequency hop across GSM band in 5 µs with phase settled by 20 µs 0.5° rms phase error at 2 GHz RF output Digitally programmable output phase RF input range up to 3.5 GHz 3-wire serial interface On-chip, low noise differential amplifier Phase noise figure of merit: -216 dBc/Hz Loop filter design possible using ADIsimPLL™ **Qualified for automotive applications**

### APPLICATIONS

**GSM/EDGE** base stations **PHS base stations** Instrumentation and test equipment

## **GENERAL DESCRIPTION**

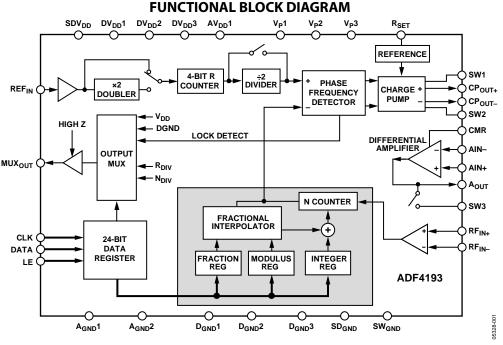

The ADF4193 frequency synthesizer can be used to implement local oscillators in the upconversion and downconversion sections of wireless receivers and transmitters. Its architecture is specifically designed to meet the GSM/EDGE lock time requirements for base stations. It consists of a low noise, digital phase frequency detector (PFD), and a precision differential charge pump. There is also a differential amplifier to convert the differential charge pump output to a single-ended voltage for the external voltage-controlled oscillator (VCO).

The  $\Sigma$ - $\Delta$  based fractional interpolator, working with the N divider, allows programmable modulus fractional-N division. Additionally, the 4-bit reference (R) counter and on-chip frequency doubler allow selectable reference signal (REFIN) frequencies at the PFD input. A complete phase-locked loop (PLL) can be implemented if the synthesizer is used with an external loop filter and a VCO. The switching architecture ensures that the PLL settles inside the GSM time slot guard period, removing the need for a second PLL and associated isolation switches. This decreases cost, complexity, PCB area, shielding, and characterization on previous ping-pong GSM PLL architectures.

#### Rev. G

**Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2005–2015 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

## ADF4193

## TABLE OF CONTENTS

| Features                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                         |

| General Description                                                                                                                  |

| Functional Block Diagram 1                                                                                                           |

| Revision History                                                                                                                     |

| Specifications                                                                                                                       |

| Timing Characteristics                                                                                                               |

| Absolute Maximum Ratings                                                                                                             |

| ESD Caution                                                                                                                          |

| Pin Configuration and Function Descriptions7                                                                                         |

| The Configuration and Pulletion Descriptions                                                                                         |

| Typical Performance Characteristics                                                                                                  |

| -                                                                                                                                    |

| Typical Performance Characteristics                                                                                                  |

| Typical Performance Characteristics    9      Theory of Operation    12                                                              |

| Typical Performance Characteristics    9      Theory of Operation    12      Reference Input Section    12                           |

| Typical Performance Characteristics    9      Theory of Operation    12      Reference Input Section    12      RF Input Stage    12 |

| Typical Performance Characteristics9Theory of Operation12Reference Input Section12RF Input Stage12Register Map15                     |

| Function Register (R3)                                         | 19 |

|----------------------------------------------------------------|----|

| Charge Pump Register (R4)                                      | 20 |

| Power-Down Register (R5)                                       | 21 |

| Mux Register (R6)                                              | 22 |

| Programming                                                    | 23 |

| Worked Example                                                 | 23 |

| Spur Mechanisms                                                | 23 |

| Power-Up Initialization                                        | 24 |

| Changing the Frequency of the PLL and the Phase Look-<br>Table | -  |

| Applications Information                                       | 26 |

| Local Oscillator for A GSM Base Station                        | 26 |

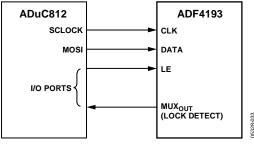

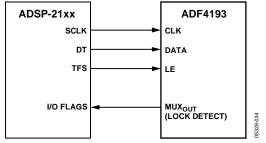

| Interfacing                                                    | 28 |

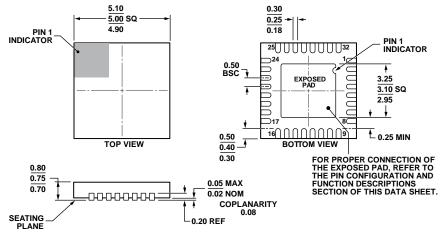

| PCB Design Guidelines for Chip Scale Package                   | 28 |

| Outline Dimensions                                             | 29 |

| Ordering Guide                                                 | 29 |

| Automotive Products                                            | 29 |

## **REVISION HISTORY**

| 1/15—Rev. F to Rev. G                           |    |

|-------------------------------------------------|----|

| Moved Revision History Section                  | 3  |

| Changes to Figure 3                             | 7  |

| Changes to PCB Design Guidelines for Chip Scale |    |

| Package Section                                 | 28 |

| Deleted CP-32-2, Figure 40                      | 29 |

| Updated Outline Dimensions                      | 29 |

| Changes to Ordering Guide                       | 29 |

|                                                 |    |

#### 3/13-Rev. E to Rev. F

| Added CP-32-2 Package     | Universal |

|---------------------------|-----------|

| Added Figure 40           |           |

| Changes to Ordering Guide |           |

## 2/13—Rev. D to Rev. E

| Changes to Phase Detector Frequency Parameter, Version C, |   |

|-----------------------------------------------------------|---|

| Table 1                                                   | 3 |

| Changes to Worked Example Section                         | 2 |

| Changes to Avoid Integer Boundary Channels Section        | 4 |

## 3/12-Rev. C to Rev. D

| Changes to Noise Characteristics Parameter, Table 1 | 4   |

|-----------------------------------------------------|-----|

| Change to Table 4                                   | 6   |

| Updated Outline Dimensions                          | .28 |

| Changes to Ordering Guide                           | .28 |

### 1/11-Rev. B to Rev. C

| Changes to Features Section         | 1 |

|-------------------------------------|---|

| Changes to Table 1                  |   |

| Changes to Table 2                  | 4 |

| Changes to Ordering Guide           |   |

| Added Automotive Products Paragraph |   |

#### 6/06—Rev A. to Rev. B

| Changes to Table 1                                          | 3  |

|-------------------------------------------------------------|----|

| Changes to Figure 32                                        | 18 |

| Changes to Power-Up Initialization Section                  | 23 |

| Changes to Timer Values for Tx Section and Timer Values for | or |

| Rx Section                                                  | 25 |

### 11/05—Rev 0. to Rev. A

| Updated Format                                                     | Universal |

|--------------------------------------------------------------------|-----------|

| Changes to Features Section                                        | 1         |

| Changes to Table 1                                                 | 3         |

| Changes to Reference Input Section                                 | 11        |

| Changes to RF N Divider Section                                    | 11        |

| Changes to the Lock Detect Section                                 | 13        |

| Changes to Figure 29                                               |           |

| Changes to the 8-Bit INT Value Section                             |           |

| Changes to Figure 33                                               |           |

| Replaced Figure 35                                                 |           |

| Changes to the $\Sigma$ - $\Delta$ and Lock Detect Modes Section . |           |

| Changes to the Power-Up Initialization Section                     | 23        |

| Changes to Table 8                                                 | 23        |

| Changes to the Local Oscillator for a GSM                          |           |

| Base Station Section                                               | 25        |

| Changes to the Timer Values for Rx Section                         | 25        |

| Changes to Figure 36                                               | 26        |

| Updates to the Outline Dimensions                                  | 28        |

| Changes to the Ordering Guide                                      |           |

|                                                                    |           |

### 4/05—Revision 0: Initial Version

## **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = SDV_{DD} = 3 V \pm 10\%, V_P1, V_P2 = 5 V \pm 10\%, V_P3 = 5.35 V \pm 5\%, AGND = DGND = OV, R_{SET} = 2.4 k\Omega, dBm$ referred to 50  $\Omega$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Parameter                               | B Version <sup>1</sup>       | C Version <sup>2</sup>       | Unit          | Test Conditions/Comments                                                          |

|-----------------------------------------|------------------------------|------------------------------|---------------|-----------------------------------------------------------------------------------|

| RF CHARACTERISTICS                      |                              |                              |               |                                                                                   |

| RF Input Frequency (RF <sub>IN</sub> )  | 0.4/3.5                      | 0.4/3.5                      | GHz min/max   | See Figure 21 for input circuit                                                   |

| RF Input Sensitivity                    | -10/0                        | -10/0                        | dBm min/max   |                                                                                   |

| Maximum Allowable Prescaler             | 470                          | 470                          | MHz max       |                                                                                   |

| Output Frequency <sup>3</sup>           |                              | 170                          |               |                                                                                   |

|                                         |                              |                              |               |                                                                                   |

| REF <sub>IN</sub> Input Frequency       | 10/300                       | 10/300                       | MHz min/max   | For f > 120 MHz, set REF/2 bit = 1. For f < 10 MHz, use a dc-coupled square wave  |

| REF <sub>IN</sub> Edge Slew Rate        | 300                          | 300                          | V/µs min      |                                                                                   |

| REF <sub>IN</sub> Input Sensitivity     | 0.7/V <sub>DD</sub>          | 0.7/V <sub>DD</sub>          | V p-p min/max | AC-coupled                                                                        |

| nei 🛛 mpar sensitivity                  |                              |                              | V max         | CMOS-compatible                                                                   |

| REF <sub>IN</sub> Input Capacitance     | 10                           | 10                           | pF max        | cinos-compatible                                                                  |

| REF <sub>IN</sub> Input Current         | ±100                         | ±100                         | μA max        |                                                                                   |

|                                         | ±100                         | ±100                         | µА тах        |                                                                                   |

| PHASE DETECTOR                          | 26                           | 20                           |               |                                                                                   |

| Phase Detector Frequency                | 26                           | 30                           | MHz max       |                                                                                   |

| CHARGE PUMP                             |                              |                              |               |                                                                                   |

| I <sub>CP</sub> Up/Down                 |                              |                              |               |                                                                                   |

| High Value                              | 6.6                          | 6.6                          | mA typ        | With $R_{SET} = 2.4 \text{ k}\Omega$                                              |

| Low Value                               | 104                          | 104                          | μA typ        | With $R_{SET} = 2.4 \text{ k}\Omega$                                              |

| Absolute Accuracy                       | 5                            | 5                            | % typ         |                                                                                   |

| R <sub>SET</sub> Range                  | 1/4                          | 1/4                          | kΩ min/max    | Nominally $R_{SET} = 2.4 \text{ k}\Omega$                                         |

| Icp Three-State Leakage                 | 1                            | 1                            | nA typ        |                                                                                   |

| I <sub>CP</sub> Up vs. Down Matching    | 0.1                          | 0.1                          | % typ         | $0.75 \text{ V} \le \text{V}_{\text{CP}} \le \text{V}_{\text{P}} - 1.5 \text{ V}$ |

| ICP VS. VCP                             | 1                            | 1                            | % typ         | $0.75 \text{ V} \le \text{V}_{\text{CP}} \le \text{V}_{\text{P}} - 1.5 \text{ V}$ |

| I <sub>CP</sub> vs. Temperature         | 1                            | 1                            | % typ         | $0.75 \text{ V} \le \text{V}_{\text{CP}} \le \text{V}_{\text{P}} - 1.5 \text{ V}$ |

| DIFFERENTIAL AMPLIFIER                  |                              |                              |               |                                                                                   |

| Input Current                           | 1                            | 1                            | nA typ        |                                                                                   |

| Output Voltage Range                    | 1.4/(V <sub>P</sub> 3 − 0.3) | 1.4/(V <sub>P</sub> 3 − 0.3) | V min/max     |                                                                                   |

| VCO Tuning Range                        | 1.8/(V <sub>P</sub> 3 - 0.8) | 1.8/(V <sub>P</sub> 3 − 0.8) | V min/max     |                                                                                   |

| Output Noise                            | 7                            | 7                            | nV/√Hz typ    | At 20 kHz offset                                                                  |

| LOGIC INPUTS                            | -                            |                              |               |                                                                                   |

| V <sub>H</sub> , Input High Voltage     | 1.4                          | 1.4                          | Vmin          |                                                                                   |

| V⊪, Input Low Voltage                   | 0.7                          | 0.7                          | V max         |                                                                                   |

| $I_{INH}$ , $I_{INL}$ , Input Current   | ±1                           | ±2                           | μA max        |                                                                                   |

|                                         | 10                           | 10                           | •             |                                                                                   |

| C <sub>IN</sub> , Input Capacitance     | 10                           | 10                           | pF max        |                                                                                   |

| LOGIC OUTPUTS                           |                              |                              | ., .          |                                                                                   |

| V <sub>OH</sub> , Output High Voltage   | V <sub>DD</sub> - 0.4        | V <sub>DD</sub> – 0.4        | V min         | $I_{OH} = 500 \mu\text{A}$                                                        |

| V <sub>OL</sub> , Output Low Voltage    | 0.4                          | 0.4                          | V max         | Ι <sub>OL</sub> = 500 μΑ                                                          |

| POWER SUPPLIES                          |                              |                              |               |                                                                                   |

| AV <sub>DD</sub>                        | 2.7/3.3                      | 2.7/3.3                      | V min/V max   |                                                                                   |

| DV <sub>DD</sub>                        | AV <sub>DD</sub>             | AV <sub>DD</sub>             |               |                                                                                   |

| V <sub>P</sub> 1, V <sub>P</sub> 2      | 4.5/5.5                      | 4.5/5.5                      | V min/V max   | $AV_{\text{DD}} \leq V_{\text{P}}1, V_{\text{P}}2 \leq 5.5 \text{ V}$             |

| V <sub>P</sub> 3                        | 5.0/5.65                     | 5.0/5.65                     | V min/V max   | $V_P1, V_P2 \le V_P3 \le 5.65 \text{ V}$                                          |

| $I_{DD} (AV_{DD} + DV_{DD} + SDV_{DD})$ | 27                           | 35                           | mA max        | 22 mA typ                                                                         |

| $I_{DD} (V_P 1 + V_P 2)$                | 27                           | 30                           | mA max        | 22 mA typ                                                                         |

| I <sub>DD</sub> (V <sub>P</sub> 3)      | 30                           | 35                           | mA max        | 24 mA typ                                                                         |

| IDD Power-Down                          | 10                           | 10                           | μA typ        |                                                                                   |

## **Data Sheet**

| Parameter                                                           | <b>B Version</b> <sup>1</sup> | C Version <sup>2</sup> | Unit       | Test Conditions/Comments                                       |

|---------------------------------------------------------------------|-------------------------------|------------------------|------------|----------------------------------------------------------------|

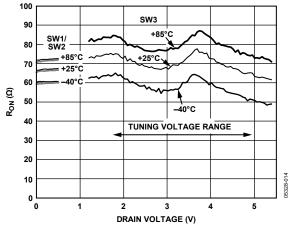

| SW1, SW2, and SW3                                                   |                               |                        |            |                                                                |

| Ron (SW1 and SW2)                                                   | 65                            | 65                     | Ωtyp       |                                                                |

| Ron SW3                                                             | 75                            | 75                     | Ωtyp       |                                                                |

| NOISE CHARACTERISTICS                                               |                               |                        |            |                                                                |

| Output                                                              |                               |                        |            |                                                                |

| 900 MHz <sup>4</sup>                                                | -108                          | -108                   | dBc/Hz typ | At 5 kHz offset and 26 MHz PFD frequency                       |

| 1800 MHz⁵                                                           | -102                          | -102                   | dBc/Hz typ | At 5 kHz offset and 13 MHz PFD frequency                       |

| Phase Noise                                                         |                               |                        |            |                                                                |

| Normalized Phase Noise<br>Floor (PN <sub>SYNTH</sub> ) <sup>6</sup> | -216                          | -216                   | dBc/Hz typ | At VCO output with dither off, PLL loop<br>bandwidth = 500 kHz |

| Normalized $1/f$ Noise (PN <sub>1_f</sub> ) <sup>7</sup>            | -110                          | -110                   | dBc/Hz typ | Measured at 10 kHz offset, normalized to 1 GHz                 |

<sup>1</sup> Operating temperature range is from –40°C to +85°C.

<sup>2</sup> Operating temperature range is from -40°C to +105°C

<sup>3</sup> The prescaler value is chosen to ensure that the RF input is divided down to a frequency that is less than this value.

$^{4}$  f<sub>REFIN</sub> = 26 MHz; f<sub>STEP</sub> = 200 kHz; f<sub>RF</sub> = 900 MHz; loop bandwidth = 40 kHz.

$^5$   $f_{\text{REF}\text{IN}}$  = 13 MHz;  $f_{\text{STEP}}$  = 200 kHz;  $f_{\text{RF}}$  = 1800 MHz; loop bandwidth = 60 kHz.

<sup>6</sup> The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log(N) (where N is the N divider value) and 10 log(f<sub>PFD</sub>). PN<sub>SYNTH</sub> = PN<sub>TOT</sub> - 10 log(f<sub>PFD</sub>) - 20 log(N).

<sup>7</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency,

<sup>7</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency,  $f_{RF}$ , and at an offset frequency,  $f_{r}$  is given by PN =  $P_{1_{c}f}$  + 10 log(10 kHz/f) + 20 log( $f_{RF}$ /1 GHz). Both the normalized phase noise floor and flicker noise are modeled in ADIsimPLL.

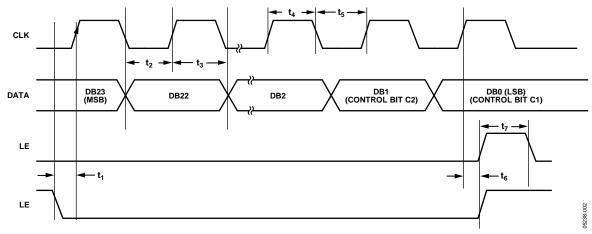

## TIMING CHARACTERISTICS

$AV_{DD} = DV_{DD} = 3 V \pm 10\%, V_P 1, V_P 2 = 5 V \pm 10\%, V_P 3 = 5.35 V \pm 5\%, AGND = DGND = GND = 0 V, R_{SET} = 2.4 k\Omega, dBm$  referred to 50  $\Omega$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 2.

| Parameter      | Limit (B Version) <sup>1</sup> | Limit (C Version) <sup>2</sup> | Unit   | Test Conditions/Comments |

|----------------|--------------------------------|--------------------------------|--------|--------------------------|

| t1             | 10                             | 10                             | ns min | LE setup time            |

| t <sub>2</sub> | 10                             | 10                             | ns min | DATA to CLOCK setup time |

| t <sub>3</sub> | 10                             | 10                             | ns min | DATA to CLOCK hold time  |

| t <sub>4</sub> | 15                             | 15                             | ns min | CLOCK high duration      |

| t5             | 15                             | 15                             | ns min | CLOCK low duration       |

| t <sub>6</sub> | 10                             | 10                             | ns min | CLOCK to LE setup time   |

| t <sub>7</sub> | 15                             | 15                             | ns min | LE pulse width           |

<sup>1</sup> Operating temperature is from  $-40^{\circ}$ C to  $+85^{\circ}$ C.

<sup>2</sup> Operating temperature is from -40°C to +105°C.

Figure 2. Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted.

#### Table 3.

| Parameter                                                    | Rating                            |

|--------------------------------------------------------------|-----------------------------------|

| AV <sub>DD</sub> to GND                                      | -0.3 V to +3.6 V                  |

| AVDD to DVDD, SDVDD                                          | –0.3 V to +0.3 V                  |

| V <sub>P</sub> to GND                                        | –0.3 V to +5.8 V                  |

| V <sub>P</sub> to AV <sub>DD</sub>                           | –0.3 V to +5.8 V                  |

| Digital I/O Voltage to GND                                   | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Analog I/O Voltage to GND                                    | -0.3 V to V <sub>P</sub> + 0.3 V  |

| REFIN, RFIN+, RFIN- to GND                                   | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Operating Temperature Range                                  |                                   |

| Industrial (B Version)                                       | -40°C to +85°C                    |

| Operating Temperature Range<br>Automotive (W Version)        | -40°C to +105°C                   |

| Storage Temperature Range                                    | –65°C to +125°C                   |

| Maximum Junction Temperature                                 | 150°C                             |

| LFCSP θ <sub>JA</sub> Thermal Impedance<br>(Paddle Soldered) | 27.3°C/W                          |

| Reflow Soldering                                             |                                   |

| Peak Temperature                                             | 260°C                             |

| Time at Peak Temperature                                     | 40 sec                            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

This device is a high performance RF integrated circuit with an ESD rating of <2 kV, and it is ESD sensitive. Proper precautions need to be taken for handling and assembly.

#### **Transistor Count**

75,800 (MOS), 545 (BJT).

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

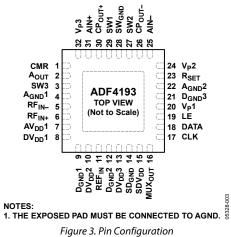

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                  |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CMR                | Common-Mode Reference Voltage for the Differential Amplifier's Output Voltage Swing. Internally biased to three-fifths of V <sub>P</sub> 3. Requires a 0.1 µF capacitor to ground.                                                           |

| 2       | Aout               | Differential Amplifier Output to Tune the External VCO.                                                                                                                                                                                      |

| 3       | SW3                | Fast-Lock Switch 3. Closed while SW3 timeout counter is active.                                                                                                                                                                              |

| 4       | A <sub>GND</sub> 1 | Analog Ground. This is the ground return pin for the differential amplifier and the RF section.                                                                                                                                              |

| 5       | RF <sub>IN-</sub>  | Complementary Input to the RF Prescaler. This point must be decoupled to the ground plane with a small bypass capacitor, typically 100 pF.                                                                                                   |

| 6       | RF <sub>IN+</sub>  | Input to the RF Prescaler. This small signal input is ac-coupled to the external VCO.                                                                                                                                                        |

| 7       | AV <sub>DD</sub> 1 | Power Supply Pin for the RF Section. Nominally 3 V. A 100 pF decoupling capacitor to the ground plane should be placed as close as possible to this pin.                                                                                     |

| 8       | DV <sub>DD</sub> 1 | Power Supply Pin for the N Divider. Should be the same voltage as $AV_{DD}1$ . A 0.1 $\mu$ F decoupling capacitor to ground should be placed as close as possible to this pin.                                                               |

| 9       | D <sub>GND</sub> 1 | Ground Return Pin for $DV_{DD}1$ .                                                                                                                                                                                                           |

| 10      | DV <sub>DD</sub> 2 | Power Supply Pin for the REF <sub>IN</sub> Buffer and R Divider. Nominally 3 V. A 0.1 μF decoupling capacitor to ground should be placed as close as possible to this pin.                                                                   |

| 11      | REFIN              | Reference Input. This is a CMOS input with a nominal threshold of $V_{DD}/2$ and a dc equivalent input resistance of 100 k $\Omega$ (see Figure 15). This input can be driven from a TTL or CMOS crystal oscillator or it can be ac-coupled. |

| 12      | D <sub>GND</sub> 2 | Ground Return Pin for $DV_{DD}2$ and $DV_{DD}3$ .                                                                                                                                                                                            |

| 13      | DV <sub>DD</sub> 3 | Power Supply Pin for the Serial Interface Logic. Nominally 3 V.                                                                                                                                                                              |

| 14      | SD <sub>GND</sub>  | Ground Return Pin for the $\Sigma$ - $\Delta$ Modulator.                                                                                                                                                                                     |

| 15      | SDV <sub>DD</sub>  | Power Supply Pin for the Digital $\Sigma$ - $\Delta$ Modulator. Nominally 3 V. A 0.1 $\mu$ F decoupling capacitor to the ground plane should be placed as close as possible to this pin.                                                     |

| 16      | MUX <sub>OUT</sub> | Multiplexer Output. This multiplexer output allows either the lock detect, the scaled RF, or the scaled reference frequency to be accessed externally (see Figure 35).                                                                       |

| 17      | CLK                | Serial Clock Input. Data is clocked into the 24-bit shift register on the CLK rising edge. This input is a high<br>impedance CMOS input.                                                                                                     |

| 18      | DATA               | Serial Data Input. The serial data is loaded MSB first with the three LSBs as the control bits. This input is a high impedance CMOS input.                                                                                                   |

| 19      | LE                 | Load Enable, CMOS Input. When LE goes high, the data stored in the shift register is loaded into the register that is selected by the three LSBs.                                                                                            |

| 20      | V <sub>P</sub> 1   | Power Supply Pin for the Phase Frequency Detector (PFD). Nominally 5 V, should be at the same voltage at V <sub>P</sub> 2. A 0.1 μF decoupling capacitor to ground should be placed as close as possible to this pin.                        |

| 21      | D <sub>GND</sub> 3 | Ground Return Pin for V₽1.                                                                                                                                                                                                                   |

| 22      | A <sub>GND</sub> 2 | Ground Return Pin for V₂2.                                                                                                                                                                                                                   |

## ADF4193

| Pin No. | Mnemonic            | Description                                                                                                                                                                                                                                  |

|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | Rset                | Connecting a resistor between this pin and GND sets the charge pump output current. The nominal voltage bias at the R <sub>SET</sub> pin is 0.55 V. The relationship between I <sub>CP</sub> and R <sub>SET</sub> is $I_{CP} = 0.25/R_{SET}$ |

|         |                     | So, with $R_{SET} = 2.4 \text{ k}\Omega$ , $I_{CP} = 104 \mu\text{A}$ .                                                                                                                                                                      |

| 24      | V <sub>P</sub> 2    | Power Supply Pin for the Charge Pump. Nominally 5 V, should be at the same voltage at V <sub>P</sub> 1. A 0.1 μF decoupling capacitor to ground should be placed as close as possible to this pin.                                           |

| 25      | AIN-                | Differential Amplifier's Negative Input Pin.                                                                                                                                                                                                 |

| 26      | CP <sub>OUT</sub> - | Differential Charge Pump's Negative Output Pin. Should be connected to AIN– and the loop filter.                                                                                                                                             |

| 27      | SW2                 | Fast Lock Switch 2. This switch is closed to $SW_{GND}$ while the SW1/SW2 timeout counter is active.                                                                                                                                         |

| 28      | $SW_{GND}$          | Common for SW1 and SW2 Switches. Should be connected to the ground plane.                                                                                                                                                                    |

| 29      | SW1                 | Fast Lock Switch 1. This switch is closed to SW <sub>GND</sub> while the SW1/SW2 timeout counter is active.                                                                                                                                  |

| 30      | CP <sub>OUT+</sub>  | Differential Charge Pump's Positive Output Pin. Should be connected to AIN+ and the loop filter.                                                                                                                                             |

| 31      | AIN+                | Differential Amplifier's Positive Input Pin.                                                                                                                                                                                                 |

| 32      | V <sub>P</sub> 3    | Power Supply Pin for the Differential Amplifier. This can range from 5.0 V to 5.5 V. A 0.1 μF decoupling capacitor to ground should be placed as close as possible to this pin. Also requires a 10 μF decoupling capacitor to ground.        |

|         | EP                  | Exposed Pad. The exposed pad must be connected to AGND.                                                                                                                                                                                      |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

| FREQ. U<br>PARAM<br>DATA F | TYPE S  | KEYWORD F<br>IMPEDANCE 5<br>MA | -     |         |          |           |

|----------------------------|---------|--------------------------------|-------|---------|----------|-----------|

| FREQ.                      | MAGS11  | ANGS11                         | FREQ. | MAGS11  | ANGS11   |           |

| 0.5                        | 0.8897  | -16.6691                       | 2.3   | 0.67107 | -75.8206 |           |

| 0.6                        | 0.87693 | -19.9279                       | 2.4   | 0.66556 | -77.6851 |           |

| 0.7                        | 0.85834 | -23.561                        | 2.5   | 0.6564  | -80.3101 |           |

| 0.8                        | 0.85044 | -26.9578                       | 2.6   | 0.6333  | -82.5082 |           |

| 0.9                        | 0.83494 | -30.8201                       | 2.7   | 0.61406 | -85.5623 |           |

| 1.0                        | 0.81718 | -34.9499                       | 2.8   | 0.5977  | -87.3513 |           |

| 1.1                        | 0.80229 | -39.0436                       | 2.9   | 0.5655  | -89.7605 |           |

| 1.2                        | 0.78917 | -42.3623                       | 3.0   | 0.5428  | -93.0239 |           |

| 1.3                        | 0.77598 | -46.322                        | 3.1   | 0.51733 | -95.9754 |           |

| 1.4                        | 0.75578 | -50.3484                       | 3.2   | 0.49909 | -99.1291 |           |

| 1.5                        | 0.74437 | -54.3545                       | 3.3   | 0.47309 | -102.208 |           |

| 1.6                        | 0.73821 | -57.3785                       | 3.4   | 0.45694 | -106.794 |           |

| 1.7                        | 0.7253  | -60.695                        | 3.5   | 0.44698 | -111.659 |           |

| 1.8                        | 0.71365 | -63.9152                       | 3.6   | 0.43589 | -117.986 |           |

| 1.9                        | 0.70699 | -66.4365                       | 3.7   | 0.42472 | -125.62  |           |

| 2.0                        | 0.7038  | -68.4453                       | 3.8   | 0.41175 | -133.291 | 8         |

| 2.1                        | 0.69284 | -70.7986                       | 3.9   | 0.41055 | -140.585 | 8-0       |

| 2.2                        | 0.67717 | -73.7038                       | 4.0   | 0.40983 | -147.97  | 05328-038 |

Figure 4. S Parameter Data for the RF Input

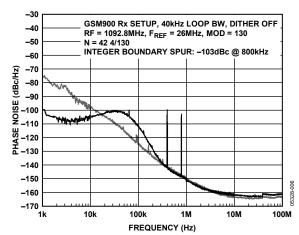

Figure 5. SSB Phase Noise Plot at 1092.8 MHz (GSM900 Rx Setup) vs. Free Running VCO Noise

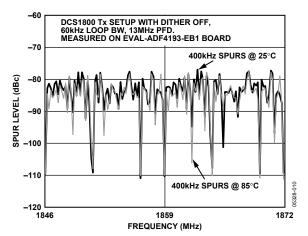

Figure 6. 400 kHz Fractional Spur Levels Across All DCS1800 Tx Channels Over Two-Integer Multiples of the PFD Reference

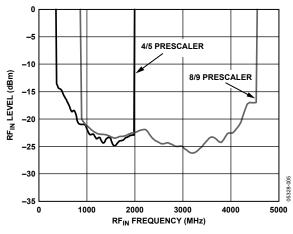

Figure 7. RF Input Sensitivity

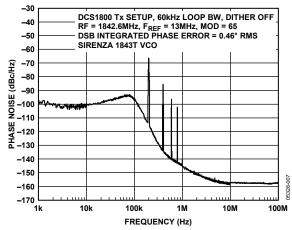

Figure 8. SSB Phase Noise Plot at 1842.6 MHz (DCS1800 Tx Setup)

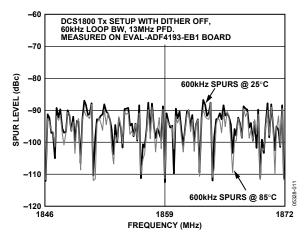

Figure 9. 600 kHz Fractional Spur Levels Across All DCS1800 Tx Channels Over Two-Integer Multiples of the PFD Reference

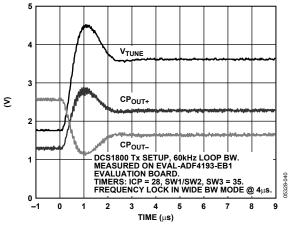

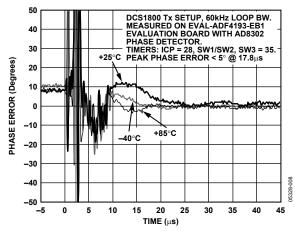

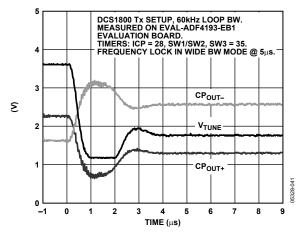

Figure 10. V<sub>TUNE</sub> Settling Transient for a 75 MHz Jump from 1818 MHz to 1893 MHz with Sirenza 1843T VCO

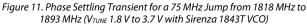

Figure 12. Differential Charge Pump Output Compliance Range and Charge Pump Mismatch with  $V_P1 = V_P2 = 5 V$

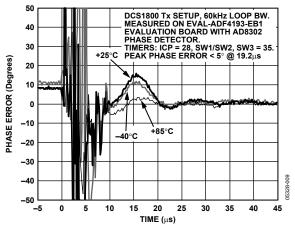

Figure 13.  $V_{TUNE}$  Settling Transient for a 75 MHz Jump Down from 1893 MHz to 1818 MHz, the Bottom of the Allowed Tuning Range with the Sirenza 1843T VCO

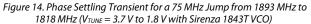

Figure 15. Tuning Range with a Sirenza 1843T VCO and a 5.5 V Differential Amplifier Power Supply Voltage

## **Data Sheet**

#### 1000 100 NOISE (nV/\Hz) 7nV/√Hz @ 20kHz 10 .11 05328-042 1 L 1k 10k 100k 1M 10M FREQUENCY (Hz)

Figure 16. Voltage Noise Density Measured at the Differential Amplifier Output

Figure 17. On Resistance of Loop Filter Switches SW1/SW2 and SW3

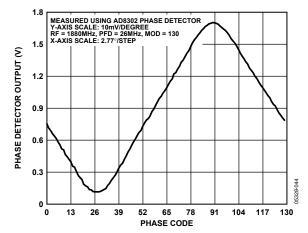

Figure 18. Detected RF Output Phase for Phase Code Sweep from 0 to MOD

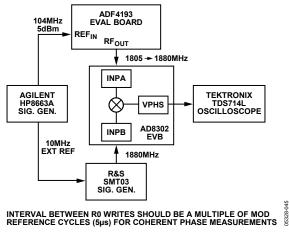

Figure 19. Test Setup for Phase Lock Time Measurement

## ADF4193

## ADF4193

## THEORY OF OPERATION

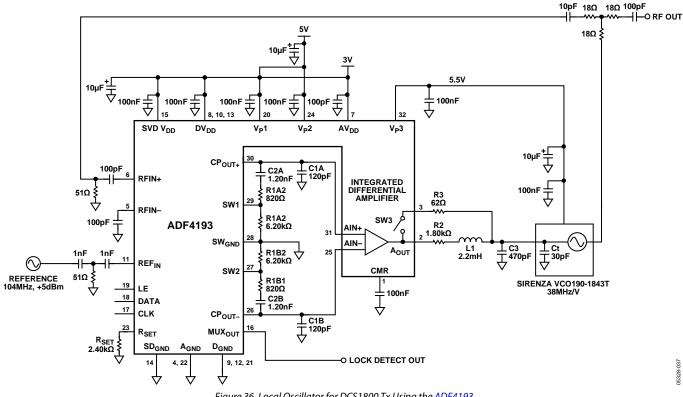

The ADF4193 is targeted at GSM base station requirements, specifically to eliminate the need for ping-pong solutions. It works based on fast lock, using a wide loop bandwidth during a frequency change and narrowing the loop bandwidth once frequency lock is achieved. Widening the loop bandwidth is achieved by increasing the charge pump current. Switches are included to change the loop filter component values to maintain stability with the changing charge pump current. The narrow loop bandwidth ensures that phase noise and spur specifications are met. A differential charge pump and loop filter topology are used to ensure that the fast lock time benefit from widening the loop bandwidth is maintained when the loop is restored to narrow bandwidth mode for normal operation.

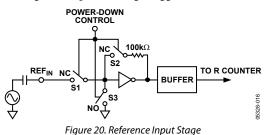

## **REFERENCE INPUT SECTION**

The reference input stage is shown in Figure 20. Switches S1 and S2 are normally closed, and S3 is normally open. During powerdown, S3 is closed, and S1 and S2 are opened to ensure that there is no loading of the REF<sub>IN</sub> pin. The falling edge of REF<sub>IN</sub> is the active edge at the positive edge triggered PFD.

## R Counter and Doubler

The 4-bit R counter allows the input reference frequency to be divided down to produce the reference clock to the phase frequency detector (PFD). A toggle flip-flop can be optionally inserted after the R counter to give a further divide-by-2. Using this option has the additional advantage of ensuring that the PFD reference clock has a 50/50 mark-space ratio. This ratio gives the maximum separation between the fast lock timer clock, which is generated off the falling edge of the PFD reference, and the rising edge, which is the active edge in the PFD. It is recommended that this toggle flip-flop be enabled for all even R divide values greater than 2. It must be enabled if dividing down a REF<sub>IN</sub> frequency that is greater than 120 MHz.

An optional doubler before the 4-bit R counter can be used for low  $REF_{\rm IN}$  frequencies, up to 20 MHz. With these programmable options, reference division ratios from 0.5 to 30 between  $REF_{\rm IN}$  and the PFD are possible.

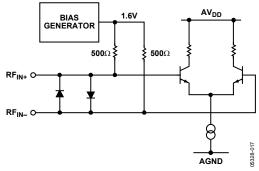

## **RF INPUT STAGE**

The RF input stage is shown in Figure 21. It is followed by a 2-stage limiting amplifier to generate the CML clock levels needed for the prescaler. Two prescaler options are selectable: a 4/5 and an 8/9. The 8/9 prescaler is selected for N divider values greater than 80.

Figure 21. RF Input Stage

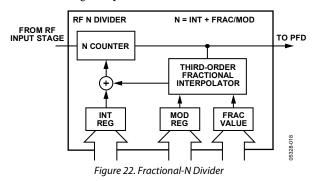

## RF N Divider

The RF N divider allows a fractional division ratio in the PLL feedback path. The integer and fractional parts of the division are programmed using separate registers, as shown in Figure 22 and described in the INT, FRAC, and MOD Relationship section. Integer division ratios from 26 to 255 are allowed and a third-order,  $\Sigma$ - $\Delta$  modulator interpolates the fractional value between the integer steps.

## INT, FRAC, and MOD Relationship

The INT, FRAC, and MOD values, programmed through the serial interface, make it possible to generate RF output frequencies that are spaced by fractions of the PFD reference frequency. The N divider value, shown inside the brackets of the following equation for the RF VCO frequency (RF<sub>OUT</sub>), is made up of an integer part (INT) and a fractional part (FRAC/MOD):

$RF_{OUT} = F_{PFD} \times [INT + (FRAC/MOD)]$

where:

$RF_{OUT}$  is the output frequency of the external VCO.  $F_{PFD}$  is the PFD reference frequency.

## Data Sheet

The value of MOD is chosen to give the desired channel step with the available reference frequency. Thereafter, program the INT and FRAC words for the desired RF output frequency. See the Worked Example section for more information.

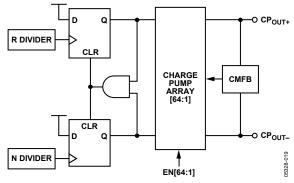

### PFD and Charge Pump

The PFD takes inputs from the R divider and N divider and produces up and down outputs with a pulse width difference proportional to the phase difference between the inputs. The charge pump outputs a net up or down current pulse of a width equal to this difference, to pump up or pump down the voltage that is integrated onto the loop filter, which in turn increases or decreases the VCO output frequency. If the N divider phase lags the R divider phase, a net up current pulse is produced that increases the VCO frequency (and thus the phase). If the N divider phase leads the R divider edge, then a net down pulse is produced to reduce the VCO frequency and phase. Figure 23 is a simplified schematic of the PFD and charge pump. The charge pump is made up of an array of 64 identical cells, each of which is fully differential. All 64 cells are active during fast lock, but only one is active during normal operation. Because a singleended control voltage is required to tune the VCO, an on-chip, differential-to-single-ended amplifier is provided for this purpose. In addition, because the phase-lock loop only controls the differential voltage generated across the charge pump outputs, an internal common-mode feedback (CMFB) loop biases the charge pump outputs at a common-mode voltage of approximately 2 V.

Figure 23. PFD and Differential Charge Pump Simplified Schematic

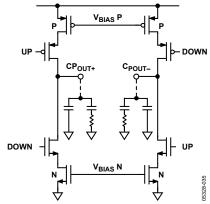

#### Differential Charge Pump

The charge pump cell (see Figure 24) has a fully differential design for best up-to-down current matching. Good matching is essential to minimize the phase offset created when switching the charge pump current from its high value (in fast lock mode) to its nominal value (in normal mode).

To pump up, the up switches are on and PMOS current is sourced out through  $CP_{OUT+}$ ; this increases the voltage on the external loop filter capacitors connected to  $CP_{OUT+}$ . Similarly, the NMOS current sink on  $CP_{OUT-}$  decreases the voltage on the external loop filter capacitors connected to  $CP_{OUT-}$ . Therefore, the differential voltage between  $CP_{OUT+}$  and  $CP_{OUT-}$  increases. To pump down, PMOS current sources out through  $CP_{OUT-}$  and ADF4193

NMOS current sinks in through CP<sub>OUT+</sub>, which decreases the (CP<sub>OUT+</sub>, CP<sub>OUT-</sub>) differential voltage. The charge pump up/ down matching is improved by an order of magnitude over the conventional single-ended charge pump that depended on the matching of two different device types. The up/down matching in this structure depends on how a PMOS matches a PMOS and an NMOS matches an NMOS.

Figure 24. Differential Charge Pump Cell with External Loop Filter Components

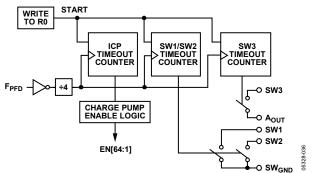

#### Fast Lock Timeout Counters

Timeout counters, clocked at one quarter the PFD reference frequency, are provided to precisely control the fast locking operation (see Figure 25). Whenever a new frequency is programmed, the fast lock timers start and the PLL locks into wide BW mode with the 64 identical 100 µA charge pump cells active (6.4 mA total). When the ICP counter times out, the charge pump current is reduced to  $1 \times$  by deselecting cells in binary steps over the next six timer clock cycles, until just one 100 µA cell is active. The charge pump current switching from 6.4 mA to 100 µA equates to an 8-to-1 change in loop bandwidth. The loop filter must be changed to ensure stability when this happens. That is the job of the SW1, SW2, and SW3 switches. The application circuit (shown in Figure 36) shows how they can be used to reconfigure the loop filter time constants. The application circuits close to short out external loop filter resistors during fast lock and open when their counters time out to restore the filter time constants to their normal values for the 100 µA charge pump current. Because it takes six timer clock cycles to reduce the charge pump current to  $1\times$ , it is recommended that both switch timers be programmed to the value of the ICP timer + 7.

Figure 25. Fast Lock Timeout Counters

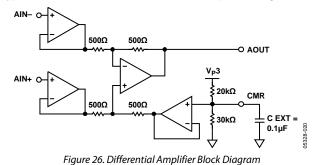

### **Differential Amplifier**

The internal, low noise, differential-to-single-ended amplifier is used to convert the differential charge pump output to a singleended control voltage for the tuning port of the VCO. Figure 26 shows a simplified schematic of the differential amplifier. The output voltage is equal to the differential voltage, offset by the voltage on the CMR pin, according to

$$V_{AOUT} = (V_{AIN+} - V_{AIN-}) + V_{CMF}$$

The CMR offset voltage is internally biased to three-fifths of V<sub>P</sub>3, the differential amplifier power supply voltage, as shown in Figure 26. Connect a 0.1  $\mu$ F capacitor to ground to the CMR pin to roll off the thermal noise of the biasing resistors.

As can be seen in Figure 15, the differential amplifier output voltage behaves according to the previous equation over a 4 V range from approximately 1.2 V minimum up to  $V_P3 - 0.3$  V. However, fast settling is guaranteed only over a tuning voltage range from 1.8 V up to  $V_P3 - 0.8$  V. This is to allow sufficient room for overshoot in the PLL frequency settling transient.

Noise from the differential amplifier is suppressed inside the PLL bandwidth. For loop bandwidths >20 kHz, the 1/f noise has a negligible effect on the PLL output phase noise. Outside the loop bandwidth, the differential amplifier's noise FM modulates the VCO. The passive filter network following the differential amplifier, shown in Figure 36, suppresses this noise contribution to below the VCO noise from offsets of 400 kHz and above. This network has a negligible effect on lock time because it is bypassed when SW3 is closed while the loop is locking.

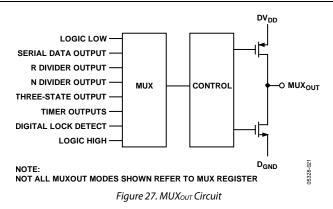

### MUXout and Lock Detect

The output multiplexer on the ADF4193 allows the user to access various internal points on the chip. The state of  $MUX_{OUT}$  is controlled by M4 to M1 in the MUX register. Figure 35 shows the full truth table. Figure 27 shows the  $MUX_{OUT}$  section in block diagram form.

## **Data Sheet**

### Lock Detect

MUX<sub>OUT</sub> can be programmed to provide a digital lock detect signal. Digital lock detect is active high. Its output goes high if there are 40 successive PFD cycles with an input error of less than 3 ns. For reliable lock detect operation with RF frequencies <2 GHz, it is recommended that this threshold be increased to 10 ns by programming Register R6. The digital lock detect goes low again when a new channel is programmed or when the error at the PFD input exceeds 30 ns for one or more cycles.

### Input Shift Register

The ADF4193 serial interface section includes a 24-bit input shift register. Data is clocked in MSB first on each rising edge of CLK. Data from the shift register is latched into one of eight control registers, R0 to R7, on the rising edge of latch enable (LE). The destination register is determined by the state of the three control bits (Control Bit C3, Control Bit C2, and Control Bit C1) in the shift register. The three LSBs are Bit DB2, Bit DB1, and Bit DB0, as shown in the timing diagram of Figure 2. The truth table for these bits is shown in Table 5. Figure 28 shows a summary of how the registers are programmed.

| Table 5. | C3, C2, | and C1 | Truth | Table |

|----------|---------|--------|-------|-------|

|----------|---------|--------|-------|-------|

|    | Control | Bits |             |          |

|----|---------|------|-------------|----------|

| С3 | C2      | C1   | Name        | Register |

| 0  | 0       | 0    | FRAC/INT    | RO       |

| 0  | 0       | 1    | MOD/R       | R1       |

| 0  | 1       | 0    | Phase       | R2       |

| 0  | 1       | 1    | Function    | R3       |

| 1  | 0       | 0    | Charge Pump | R4       |

| 1  | 0       | 1    | Power-Down  | R5       |

| 1  | 1       | 0    | Mux         | R6       |

| 1  | 1       | 1    | Test Mode   | R7       |

## **REGISTER MAP**

#### FRAC/INT REGISTER (R0)

| RESERVED |      |      | 8-BIT | RF INT V | /ALUE |      |      |      |      |      |      |      | 12-B | IT RF F | RAC VA | LUE |     |     |     |     | c      | ONTRO  | )L     |

|----------|------|------|-------|----------|-------|------|------|------|------|------|------|------|------|---------|--------|-----|-----|-----|-----|-----|--------|--------|--------|

| DB23     | DB22 | DB21 | DB20  | DB19     | DB18  | DB17 | DB16 | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9     | DB8    | DB7 | DB6 | DB5 | DB4 | DB3 | DB2    | DB1    | DB0    |

| 0        | N8   | N7   | N6    | N5       | N4    | N3   | N2   | N1   | F12  | F11  | F10  | F9   | F8   | F7      | F6     | F5  | F4  | F3  | F2  | F1  | C3 (0) | C2 (0) | C1 (0) |

#### MOD/R REGISTER (R1)

| DBB    | DBB   |          |           | DBB     |      |               |              | DBB  |      |      |      |      |      |         |       |     |     |     |     | DBB |        |               |        |

|--------|-------|----------|-----------|---------|------|---------------|--------------|------|------|------|------|------|------|---------|-------|-----|-----|-----|-----|-----|--------|---------------|--------|

| CP ADJ | REF/2 | RESERVED | PRESCALER | DOUBLER |      | 4-BIT<br>COUI | RF R<br>NTER |      |      |      |      |      | 1    | 2-BIT M | ODULU | S   |     |     |     |     | c      | ONTRO<br>BITS | L      |

| DB23   | DB22  | DB21     | DB20      | DB19    | DB18 | DB17          | DB16         | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9     | DB8   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2    | DB1           | DB0    |

| F5     | F4    | 0        | F2        | F1      | R4   | R3            | R2           | R1   | M12  | M11  | M10  | М9   | M8   | M7      | M6    | M5  | M4  | M3  | M2  | M1  | C3 (0) | C2 (0)        | C1 (1) |

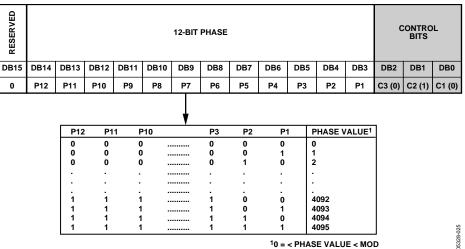

### PHASE REGISTER (R2)

| RESERVED |      |      |      |      |      | 12-BIT | PHASE |     |     |     |     | DBB | c      | ONTRO  | )L     |

|----------|------|------|------|------|------|--------|-------|-----|-----|-----|-----|-----|--------|--------|--------|

| DB15     | DB14 | DB13 | DB12 | DB11 | DB10 | DB9    | DB8   | DB7 | DB6 | DB5 | DB4 | DB3 | DB2    | DB1    | DB0    |

| 0        | P12  | P11  | P10  | P9   | P8   | P7     | P6    | P5  | P4  | P3  | P2  | P1  | C3 (0) | C2 (1) | C1 (0) |

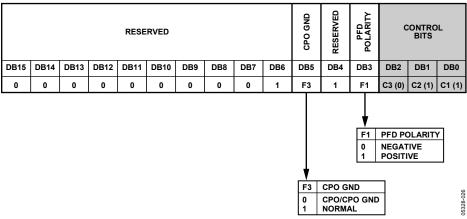

### FUNCTION REGISTER (R3)

|      |      |      |      | RESE | RVED |     |     |     |     | CPO GND | RESERVED | PFD<br>POLARITY | c      | CONTRO<br>BITS | L      |

|------|------|------|------|------|------|-----|-----|-----|-----|---------|----------|-----------------|--------|----------------|--------|

| DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5     | DB4      | DB3             | DB2    | DB1            | DB0    |

| 0    | 0    | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 1   | F3      | 1        | F1              | C3 (0) | C2 (1)         | C1 (1) |

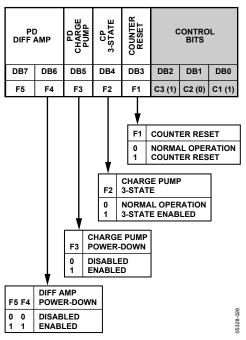

#### **CHARGE PUMP REGISTER (R4)**

|      |      |      |      | RESE | RVED |      |      |      |      |      | 9-BIT TIMEOUT COUNTER |      |      |     |     |     |     |     |     |     | С      | ONTROL<br>BITS |        |

|------|------|------|------|------|------|------|------|------|------|------|-----------------------|------|------|-----|-----|-----|-----|-----|-----|-----|--------|----------------|--------|

| DB23 | DB22 | DB21 | DB20 | DB19 | DB18 | DB17 | DB16 | DB15 | DB14 | DB13 | DB12                  | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2    | DB1            | DB0    |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | C9   | C8                    | C7   | C6   | C5  | C4  | C3  | C2  | C1  | F2  | F1  | C3 (1) | C2 (0)         | C1 (0) |

### **POWER-DOWN REGISTER (R5)**

|         |    |     | CP<br>3-STATE | COUNTER<br>RESET | c      | ONTRO<br>BITS | )L     |

|---------|----|-----|---------------|------------------|--------|---------------|--------|

| DB7 DB6 |    | DB5 | DB4           | DB3              | DB2    | DB1           | DB0    |

| F5      | F4 | F3  | F2            | F1               | C3 (1) | C2 (0)        | C1 (1) |

#### MUX REGISTER (R6)

| LO   | SIGMA-DELTA<br>AND<br>LOCK DETECT MODES |      |      |      | RESERVED |     |     |     |     |     | ( <sub>OUT</sub> |     | CONTROL<br>BITS |        |        |

|------|-----------------------------------------|------|------|------|----------|-----|-----|-----|-----|-----|------------------|-----|-----------------|--------|--------|

| DB15 | DB14                                    | DB13 | DB12 | DB11 | DB10     | DB9 | DB8 | DB7 | DB6 | DB5 | DB4              | DB3 | DB2             | DB1    | DB0    |

| M13  | M12                                     | M11  | M10  | 0    | 0        | 0   | 0   | 0   | M4  | М3  | M2               | M1  | C3 (1)          | C2 (1) | C1 (0) |

### **TEST MODE REGISTER (R7)**

|      | RESERVED |      |      |      |      |     |     |     |     |     |     |     | CONTROL<br>BITS |        |        |

|------|----------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----------------|--------|--------|

| DB15 | DB14     | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2             | DB1    | DB0    |

| 0    | 0        | 0    | 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | C3 (1)          | C2 (1) | C1 (1) |

DBB = DOUBLE BUFFERED BIT(S)

## FRAC/INT REGISTER (R0)

| RESERVED |      |      | 8-BIT I | RF INT ' | VALUE |      |       |      |        |      |        |       | 12-E | IT RF F | RAC VA | LUE      |     |       |        |        | c       | ONTRO<br>BITS | L         |

|----------|------|------|---------|----------|-------|------|-------|------|--------|------|--------|-------|------|---------|--------|----------|-----|-------|--------|--------|---------|---------------|-----------|

| DB23     | DB22 | DB21 | DB20    | DB19     | DB18  | DB17 | DB16  | DB15 | DB14   | DB13 | DB12   | DB11  | DB10 | DB9     | DB8    | DB7      | DB6 | DB5   | DB4    | DB3    | DB2     | DB1           | DB0       |

| 0        | N8   | N7   | N6      | N5       | N4    | N3   | N2    | N1   | F12    | F11  | F10    | F9    | F8   | F7      | F6     | F5       | F4  | F3    | F2     | F1     | C3 (0)  | C2 (0)        | C1 (0)    |

|          |      |      |         |          |       |      | _     |      |        |      |        |       |      |         |        |          |     |       |        |        |         |               |           |

|          |      |      |         |          |       |      |       | F12  | F11    |      | F10    |       | F    | -       | F2     | F1       | 1   |       | CTIONA | L VALU | E (FRAC | ;)            |           |

|          |      |      |         |          |       |      |       | )    | 0<br>0 |      | 0<br>0 |       | 0    | 1       | 0<br>0 | 0<br>1   |     | 0     |        |        |         |               |           |

|          |      |      |         |          |       |      | - i   |      | Ō      |      | Ō      |       | Ő    | 1       | 1      | Ó        |     | 2     |        |        |         |               |           |

|          |      |      |         |          |       |      |       | כ    | 0      |      | 0      |       | 0    | 1       | 1      | 1        |     | 3     |        |        |         |               |           |

|          |      |      |         |          |       |      |       |      | •      |      | •      | ••••• | •    |         | •      | •        |     | •     |        |        |         |               |           |

|          |      |      |         |          |       |      |       |      | •      |      | •      |       | •    |         | •      | •        |     | •     |        |        |         |               |           |

|          |      |      |         |          |       |      |       | 1    | 1      |      | 1      |       | . 1  |         | 0      | 0        |     | 4092  |        |        |         |               |           |

|          |      |      |         |          |       |      | ·   · | 1    | 1      |      | 1      |       | 1    |         | Ō      | 1        |     | 4093  |        |        |         |               |           |

|          |      |      |         |          |       |      | ·   · | 1    | 1      |      | 1      |       | 1    |         | 1      | 0        |     | 4094  |        |        |         |               |           |

|          |      |      |         |          |       |      |       | 1    | 1      |      | 1      |       | 1    |         | 1      | 1        |     | 4095  |        |        |         |               |           |

|          |      |      |         |          |       |      |       |      |        |      |        |       |      |         |        |          |     | 0 = < | FRAC < | MOD    |         |               |           |

|          |      |      |         | ł        |       |      |       |      |        |      |        |       |      |         |        |          |     |       |        |        |         |               |           |

|          |      | N    | 18      | N7       | N     | 16   | N5    | N4   |        | N3   | N2     | Ν     | 1    | INT     | EGER V | ALUE (IN | IT) |       |        |        |         |               |           |

|          |      | 0    |         | 0        | 0     |      | 1     | 1    |        | 0    | 1      | 0     |      | 26      |        |          |     |       |        |        |         |               |           |

|          |      | ·    |         | -        | •     |      | •     | •    |        | •    | ·      | •     |      | •       |        |          |     |       |        |        |         |               |           |

|          |      | ·    |         | •        | •     |      | •     | •    |        | •    | •      | •     |      | 1.      |        |          |     |       |        |        |         |               | ~         |

|          |      | 1    |         | 1        | . 1   |      | 1     | 1    |        | 1    | 1      | 1     |      | 255     |        |          |     |       |        |        |         |               | 05328-023 |

|          |      |      |         |          |       |      |       |      |        |      |        |       |      |         |        |          |     |       |        |        |         |               | 532       |

Figure 29. FRAC/INT Register (R0)

R0, the FRAC/INT register, is used to program the synthesizer output frequency. On the next PFD cycle following a write to R0, the N divider section is updated with the new INT and FRAC values. At the same time, the PLL automatically enters fast lock mode and the charge pump current is increased to its maximum value and stays at this value until the ICP timeout counter times out, and switches SW1, SW2, and SW3 closed and remains closed until the SW1, SW2, and SW3 timeout counters time out.

Once all registers are programmed during the initialization sequence (see Table 8), all that is required thereafter to program a new channel is a write to R0. However, as described in the Programming section, it can also be desirable to program R1 and R2 register settings on a channel-by-channel basis. These settings are double buffered by the write to R0. This means that while the data is loaded through the serial interface on the respective R1 and R2 write cycles, the synthesizer is not updated with their data until the next write to Register R0.

### **Control Bits**

The three LSBs, Control Bit C3, Control Bit C2, and Control Bit C1, should be set to 0, 0, 0, respectively, to select R0, the FRAC/INT register.

#### **Reserved Bit**

Bit DB23 is reserved and must be set to 0.

#### 8-Bit INT Value

These eight bits set the INT value, which determines the integer part of the feedback division factor. All integer values from 26 to 255 are allowed. See the Worked Example section.

#### 12-Bit FRAC Value

The 12 FRAC bits set the numerator of the fraction that is input to the  $\Sigma$ - $\Delta$  modulator. This, along with INT, specifies the new frequency channel that the synthesizer locks to, as shown in the Worked Example section. FRAC values from 0 to MOD – 1 cover channels over a frequency range equal to the PFD reference frequency.

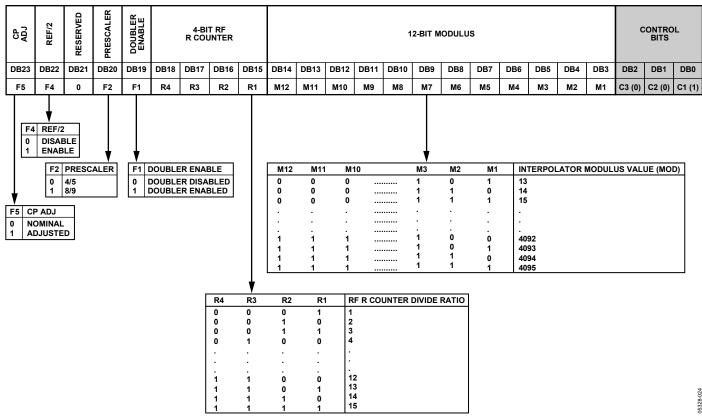

## MOD/R REGISTER (R1)

#### Figure 30. MOD/R Register (R1)

This register is used to set the PFD reference frequency and the channel step size, which is determined by the PFD frequency divided by the fractional modulus. Note that the MOD, R counter, REF/2, CP ADJ, and doubler enable bits are double buffered. They do not take effect until the next write to R0 (FRAC/INT register) is complete.

## **Control Bits**

With C3, C2, and C1 set to 0, 0, 1, respectively, the MOD/R register (R1) is programmed.

## CP ADJ

When this bit is set to 1, the charge pump current is scaled up 25% from its nominal value on the next write to R0. When this bit is set to 0, the charge pump current stays at its nominal value on the next write to R0. See the Programming section for more information on how this feature can be used.

## REF/2

Setting this bit to 1 inserts a divide-by-2, toggle flip-flop between the R counter and PFD, which extends the maximum  $REF_{IN}$  input rate.

#### **Reserved Bit**

Reserved Bit DB21 must be set to 0.

#### **Doubler Enable**

Setting this bit to 1 inserts a frequency doubler between  $REF_{IN}$  and the 4-bit R counter. Setting this bit to 0 bypasses the doubler.

#### 4-Bit RF R Counter

It allows the  $REF_{IN}$  frequency to be divided down to produce the reference clock to the PFD. All integer values from 1 to 15 are allowed. See the Worked Example section.

## 12-Bit Interpolator Modulus

For a given PFD reference frequency, the fractional denominator or modulus sets the channel step resolution at the RF output. All integer values from 13 to 4095 are allowed. See the Programming section for additional information and guidelines for selecting the value of MOD.

## ADF4193

## PHASE REGISTER (R2)

Figure 31. Phase Register (R2)

#### 12-Bit Phase

The phase word sets the seed value of the  $\Sigma$ - $\Delta$  modulator. It can be programmed to any integer value from 0 to MOD. As the phase word is swept from 0 to MOD, the phase of the VCO output sweeps over a 360° range in steps of 360°/MOD.

Note that the phase bits are double buffered. They do not take effect until the LE of the next write to R0 (FRAC/INT register). Therefore, if it is desired to change the phase of the VCO output frequency, it is necessary to rewrite the INT and FRAC values to R0, following the write to R2.

The output of a fractional-N PLL can settle to any one of the MOD possible phase offsets with respect to the reference, where MOD is the fractional modulus.

If it is desired to keep the output at the same phase offset with respect to the reference, each time that particular output frequency is programmed, then the interval between writes to R0 must be an integer multiple of MOD reference cycles.

If it is desired to keep the outputs of two ADF4193-based synthesizers phase coherent with each other, but not necessarily with their common reference, then it is only required to ensure that the write to R0 on both chips is performed during the same reference cycle. The interval between R0 writes in this case does not have to be an integer multiple of the MOD cycles.

### **Reserved Bit**

The reserved bit, Bit DB15, should be set to 0.

## **FUNCTION REGISTER (R3)**

Figure 32. Function Register (R3)

R3, the function register (C3, C2, C1 set to 0, 1, 1, respectively), only needs to be programmed during the initialization sequence (see Table 8).

## CPO GND

When the CPO GND bit is low, the charge pump outputs are internally pulled to ground. This is invoked during the initialization sequence to discharge the loop filter capacitors. For normal operation, this bit should be high.

## **PFD Polarity**

This bit should be set to 1 for positive polarity and set to 0 for negative polarity.

### **Reserved Bits**

The Bit DB15 to Bit DB6 are reserved bits and should be programmed to hex code 001, and Reserved Bit DB4 should be set to 1.

## **CHARGE PUMP REGISTER (R4)**

|      | RESERVED                                         |   |   |   |   |   |   |     | 9-BIT TIMEOUT COUNTER |                                    |    |       |    |    |    |        |            | TIMER<br>SELECT      |       |              |        |         |                    |

|------|--------------------------------------------------|---|---|---|---|---|---|-----|-----------------------|------------------------------------|----|-------|----|----|----|--------|------------|----------------------|-------|--------------|--------|---------|--------------------|

| DB23 | 323 DB22 DB21 DB20 DB19 DB18 DB17 DB16 DB15 DB14 |   |   |   |   |   |   |     | DB14                  | DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB |    |       |    |    |    | DB6    | DB5        | DB4                  | DB3   | DB2          | DB1    | DB0     |                    |

| 0    | 0                                                | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 1                     | C9                                 | C8 | C7    | C6 | C5 | C4 | C3     | C2         | C1                   | F2    | F1           | C3 (1) | C2 (0)  | C1 (0)             |

|      |                                                  |   |   |   |   |   |   |     |                       |                                    |    |       |    |    |    |        |            | 0 SV<br>1 SV<br>0 IC |       |              |        |         |                    |

|      |                                                  |   |   |   |   |   |   | C   | 9 (                   | 28                                 | C7 |       | C3 | C2 | 2  | C1     | TIMEO      | UT COI               | UNTER | xPFD (       | CYCLES | DEL     | AY µs <sup>1</sup> |

|      |                                                  |   |   |   |   |   |   | 0   | 0                     |                                    | 0  |       | 0  | 0  |    | 0      | 0          |                      |       | 0            |        | 0       |                    |

|      |                                                  |   |   |   |   |   |   | 0   | 0                     |                                    | 0  |       | 0  | 0  |    | 1<br>0 | 1          |                      |       | 4<br>8       |        | 0.15    |                    |

|      |                                                  |   |   |   |   |   |   | 0   | (                     |                                    | 0  |       | 0  | 1  |    | 1      | 2<br>3     |                      |       | o<br>12      |        | 0.30    |                    |

|      |                                                  |   |   |   |   |   |   |     |                       |                                    |    |       |    |    |    | .      |            |                      |       |              |        |         |                    |

|      |                                                  |   |   |   |   |   |   | 1.  |                       |                                    |    |       |    |    |    | .      |            |                      |       |              |        |         |                    |

|      |                                                  |   |   |   |   |   |   | · · |                       |                                    | ÷  |       | :  |    |    | .      |            |                      |       |              |        | 78.15   | .                  |

|      |                                                  |   |   |   |   |   |   |     | 1                     |                                    | 1  | ••••• | 1  | 0  |    | 0      | 508<br>509 |                      |       | 2032<br>2036 |        | 78.1    |                    |

|      |                                                  |   |   |   |   |   |   |     | 1                     |                                    | 1  |       | i  | 1  |    | o I    | 510        |                      |       | 2040         |        | 78.46   |                    |

|      |                                                  |   |   |   |   |   |   |     | -                     |                                    | 1  |       | 1  | 1  |    | 1      | 511        |                      |       | 2044         |        | 78.61   |                    |

|      |                                                  |   |   |   |   |   |   |     |                       |                                    |    |       |    |    |    |        |            |                      |       | 1D           | ELAY W | ITH 26N | IHz PFD            |

Figure 33. Charge Pump Register (R4)

### **Reserved Bits**

Bit DB23 to Bit DB14 are reserved and should be set to hex code 001 for normal operation.

#### 9-Bit Timeout Counter

These bits are used to program the fast lock timeout counters. The counters are clocked at one-quarter the PFD reference frequency, therefore, their time delay scales with the PFD frequency according to

*Delay(s)* = (*Timeout Counter Value* × 4)/(*PFD Frequency*)

For example, if 35 were loaded with timer select (00) with a 13 MHz PFD, then SW1/SW2 would be switched after

$(35 \times 4)/13$  MHz = 10.8 µs

#### **Timer Select**